Turinys:

- 1 veiksmas: pridėkite šaltinių ir pasirinkite „Pridėti arba sukurti modeliavimo šaltinius“

- 2 veiksmas: sukurkite failą pavadinimu Enable_sr_tb

- 3 žingsnis: sukurkite „Testbench“failą

- 4 veiksmas: nustatykite „Enable_sr_tb“kaip aukščiausią modeliavimo lygį

- 5 veiksmas: paleiskite sintezę ir elgesio modeliavimą

- 6 žingsnis: Įvertinkite modeliavimo rezultatą

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:48.

- Paskutinį kartą keistas 2025-01-23 14:59.

Aš padariau šį modeliavimo projektą internetinei klasei. Projektą parašė „Verilog“. Mes naudosime modeliavimą „Vivado“, kad vizualizuotume bangos formą „enable_sr“(įgalinimo skaitmuo) iš anksčiau sukurto chronometro projekto. Be to, mes naudosime sistemos užduotį, kad parodytume projektavimo metu padarytas klaidas.

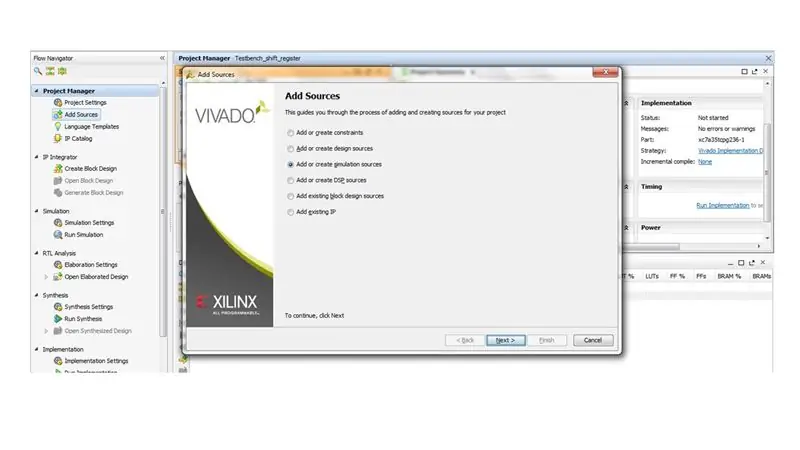

1 veiksmas: pridėkite šaltinių ir pasirinkite „Pridėti arba sukurti modeliavimo šaltinius“

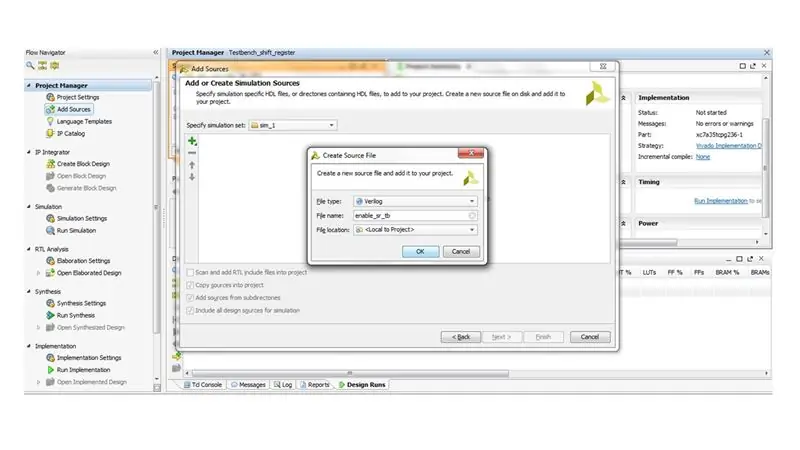

2 veiksmas: sukurkite failą pavadinimu Enable_sr_tb

3 žingsnis: sukurkite „Testbench“failą

1. Importuokite modulį enable_sr iš chronometro projekto. Tai yra failas, kurį norime imituoti

2. Sukurkite testbench modulį enable_sr_tb ();

3. Įveskite modulio enable_sr () įėjimus ir išėjimus. Atminkite, kad „enable_sr“įvestys dabar yra registro tipo, o išėjimai tampa grynojo tipo.

4. Įveskite bandomą įrenginį (uut), kuris yra enable_sr

5. Sukurkite laikrodį, kurio laikotarpis (T) yra 20ns

6. Naudokite sąlyginį teiginį, kad sukurtumėte klaidų tikrinimo sistemą. Šiame pavyzdyje norime patikrinti, ar yra aktyvių daugiau nei vienas skaitmuo.

Pastaba: pradiniame failo enable_sr () faile šabloną turime inicijuoti kaip 4’b0011, kad būtų sukurti du skaitmenys, kad būtų sukurta klaida

7. Norėdami parodyti klaidą, naudokite sistemos užduotį $ display

8. Norėdami užbaigti simuliaciją 400ns laiku, naudokite sistemos užduotį $ finish

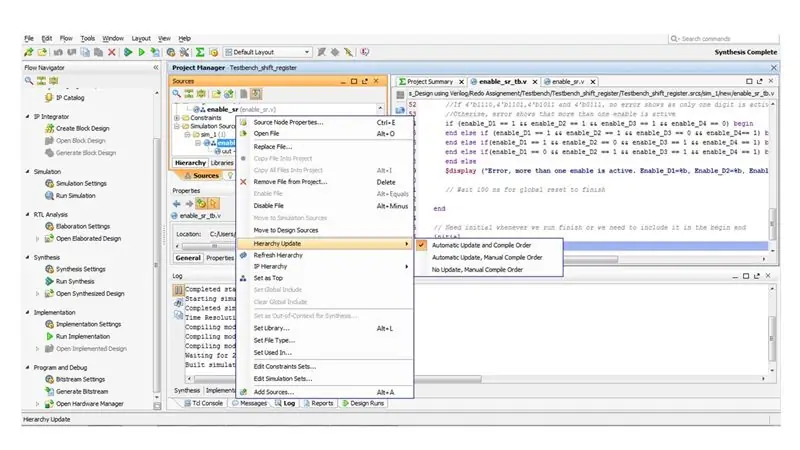

4 veiksmas: nustatykite „Enable_sr_tb“kaip aukščiausią modeliavimo lygį

5 veiksmas: paleiskite sintezę ir elgesio modeliavimą

- Prieš vykdydami elgesio modeliavimą, paleiskite sintezę, kad įsitikintumėte, jog testbench faile ir bandomojo failo vienete nėra sintaksės klaidų

- Vykdykite elgesio modeliavimą

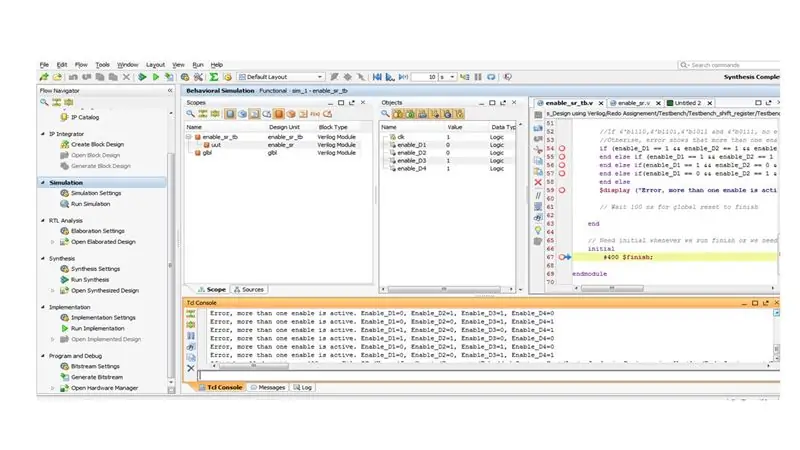

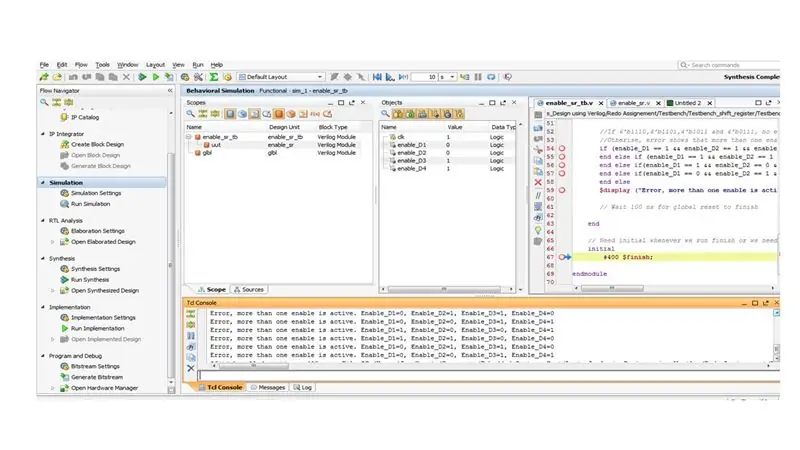

6 žingsnis: Įvertinkite modeliavimo rezultatą

Pamatysite modeliavimo langus. Jame yra skirtingos plokštės.

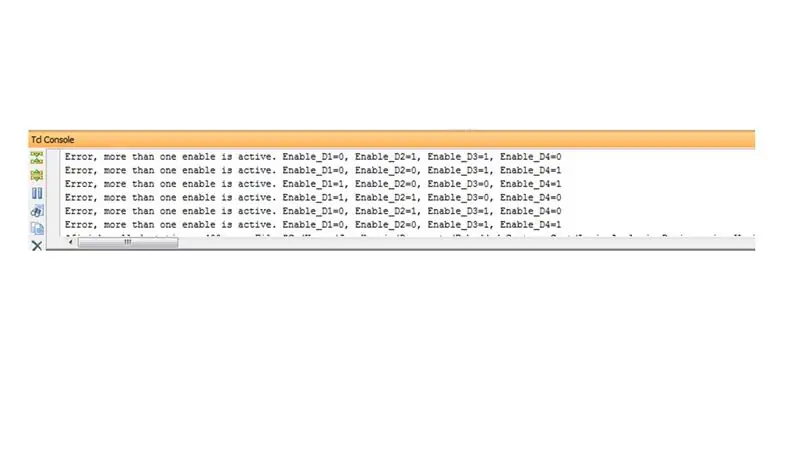

Konsolės skydelyje pamatysite klaidos pranešimą. Tai rodo, kad modeliavimo laikotarpiu aktyvūs daugiau nei vienas skaitmuo.

Apimtyje taip pat galite pamatyti bangos formą

Pridedamas projekto failas.

Rekomenduojamas:

Kaip naudoti ESP8266 kaip žiniatinklio serverį: 5 žingsniai

Kaip naudotis ESP8266 kaip žiniatinklio serveriu: Sveiki, šiuo metu naudoju „Windows 10“, „NodeMCU 1.0“, čia yra mano naudojamos programinės įrangos sąrašas ir diegimo vadovai, kurių laikiausi: „Arduino IDE“Papildomos „esp8266“lentos „SpiffLibrary“: „Websocket“naudoju „NodeMCU“kaip serverį aptarnauju HTML failą

Kaip naudoti žingsninį variklį kaip rotacinį kodavimo įrenginį ir OLED ekraną žingsniams: 6 žingsniai

Kaip naudoti žingsninį variklį kaip rotacinį kodavimo įrenginį ir OLED ekraną žingsniams: Šioje pamokoje sužinosime, kaip sekti žingsninio variklio žingsnius OLED ekrane. Žiūrėkite demonstracinį vaizdo įrašą. Originalios pamokos kreditas skirtas „YouTube“naudotojui " sky4fly "

Kaip naudoti „Android“telefoną kaip internetinę kamerą naudojant „Skype“: 5 žingsniai

Kaip naudoti „Android“telefoną kaip internetinę kamerą naudojant „Skype“: Yra senas posakis, kad nuotrauka verta tūkstančio žodžių … ir yra naujas posakis, kad vaizdo įrašas yra vertas milijono. Dabar tai gali atrodyti perdėta, tačiau yra didžiulis skirtumas tarp pokalbio su kam nors ir skambučio

Visuino Kaip naudoti mygtuką kaip įvestį valdyti tokius dalykus kaip LED: 6 žingsniai

Visuino Kaip naudoti mygtuką kaip įvestį valdyti tokius dalykus kaip LED: Šioje pamokoje mes sužinosime, kaip įjungti ir išjungti šviesos diodą naudojant paprastą mygtuką ir Visuino. Žiūrėkite demonstracinį vaizdo įrašą

Kaip naudoti „Wiimote“kaip kompiuterio pelę naudojant žvakes kaip jutiklį !!: 3 žingsniai

Kaip naudoti „Wiimote“kaip kompiuterio pelę naudojant žvakes kaip jutiklį !!: Šis vadovas parodys, kaip susieti „Wii Remote“(„Wiimote“) su kompiuteriu ir naudoti kaip pelę