Turinys:

- 1 veiksmas: Skaitmeninio sekos naudotojo valdymas

- 2 žingsnis: techninė informacija

- 3 žingsnis: techninė informacija

- 4 žingsnis: 7 segmentų laikrodžio daliklis

- 5 žingsnis: dūžių per minutę laikrodžio daliklis

- 6 žingsnis: Laikrodžio daliklis

- 7 veiksmas: paleiskite/pristabdykite/pasirinkite būsenos mašiną

- 8 veiksmas: paleiskite/pristabdykite/pasirinkite būsenos mašiną

- 9 veiksmas: išveskite FSM

- 10 veiksmas: išveskite FSM

- 11 veiksmas: Pastaba Priskirti

- 12 veiksmas: išvesties pasirinkimas

- 13 žingsnis: „Square Wave“gen

- 14 žingsnis: 7 segmentų ekranas

- 15 žingsnis: galutinis pasirinkimas

- 16 veiksmas: išoriniai įrenginiai: DAC

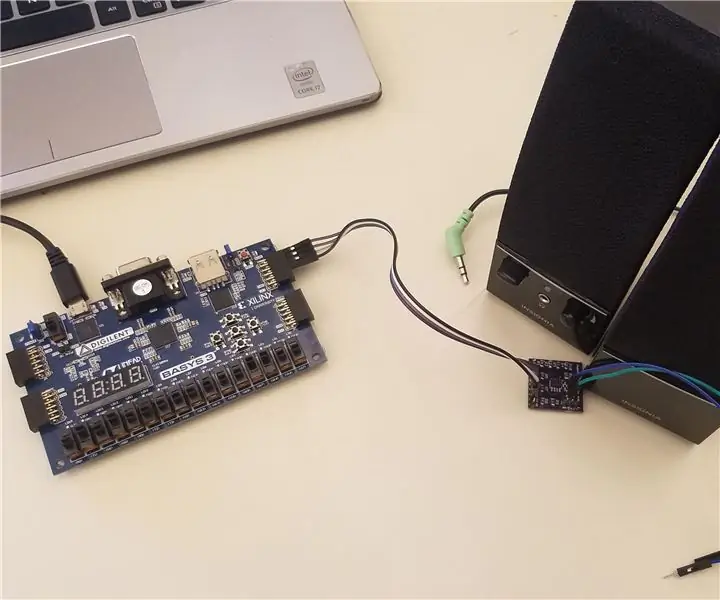

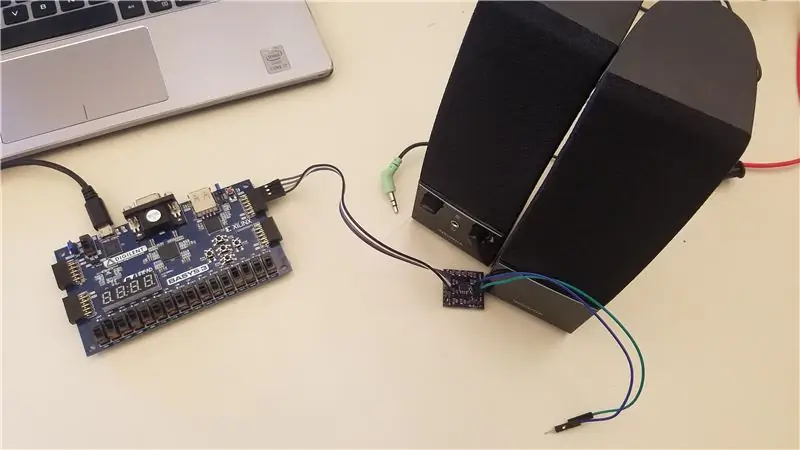

- 17 žingsnis: išoriniai įrenginiai: garsiakalbis

- 18 veiksmas: vaizdo įrašo demonstracija

- 19 veiksmas: VHDL kodas

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:49.

- Paskutinį kartą keistas 2025-06-01 06:09.

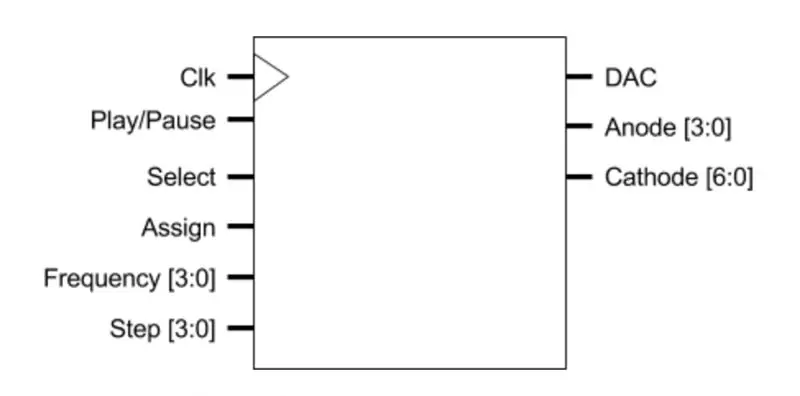

CPE 133, Cal Poly San Luis Obispo

Projekto kūrėjai: Jaysonas Johnstonas ir Bjornas Nelsonas

Šiuolaikinėje muzikos pramonėje vienas iš dažniausiai naudojamų „instrumentų“yra skaitmeninis sintezatorius. Kiekvienas muzikos žanras-nuo hip-hopo iki popso ir net kantri-studijoje naudoja skaitmeninį sintezatorių, kad sukurtų ritmus ir garsus, kurių reikia jų muzikai atgaivinti. Šioje pamokoje mes sukursime labai paprastą sintezatorių su „Basys 3 FPGA“plokšte.

Sintezatorius galės groti keturias pasirinktas ketvirčio natas pastoviu dūžių skaičiumi per minutę. Vartotojai naudosis jungikliais, kad kiekvieną ketvirčio natą priskirtų muzikinei aikštei. Šiam projektui mes naudojame 4 bitų skaitmeninį analoginį keitiklį (DAC), kad išvestis iš plokštės būtų konvertuojama į analoginį signalą. Tada DAC išvestis bus tiekiama į standartinį kompiuterio garsiakalbį, sukuriant mūsų muziką. Galimos šešiolika diskrečių aikštelių. Mes apribosime savo sintezatorių iki vienos oktavos iš 12 natų, kurios yra tarp vidurio C (261,6 Hz) ir B4 (493,9 Hz). Vartotojas taip pat turės galimybę vienu metu priskirti kelias natas, taip pat priskirti poilsį, paspausdamas priskirti, o nė vienas aukščio jungiklis nebus perkeltas aukštyn. Pasirinkus ir grojant kiekvieną natą, raidžių pastaba rodoma 7 segmentų ekrane. Mes taip pat naudosime tris mygtukus lentoje, vieną muzikai paleisti ir pristabdyti, vieną sintezatoriaus nustatymui iš naujo ir įjungimą į „atrankos“režimą, o trečiąjį - kiekvienai natai priskirti aukštį pasirinkimo režimu.

Kai vartotojas bus patenkintas pasirinktu natomis ir paspaudęs grojimo mygtuką, sintezatorius pakartos kiekvieną natą iš eilės, kol vartotojas paspaus pauzę arba pasirinkite.

Čia yra reikalingos įrangos sąrašas:

- „Vivado“(arba bet kuri VHDL darbo vieta)

- „Basys 3“ar panaši FPGA plokštė

- Skaitmeninis į analoginį keitiklis (mažiausiai 4 bitai)

- Garsiakalbis su ausinių lizdu

- Laidų laidai

1 veiksmas: Skaitmeninio sekos naudotojo valdymas

Toliau pateikiami skaitmeninio sekos valdiklio veiksmai. Skaitmeninis sekų sekiklis palaiko 12 skirtingų garsų atkūrimą (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), kurių diapazonas yra nuo 261,6 Hz iki 493,9 Hz.

1. Paspauskite kairįjį mygtuką, kad įjungtumėte plokštę į pasirinkimo režimą. Įjungus šį režimą, į kairę esantys 4 jungikliai (13-16 jungikliai) bus naudojami skirtingai aukščio vertei išsaugoti.

2. Norėdami pasirinkti, įjunkite vieną iš kairiųjų jungiklių, tada naudokite dešiniausius 4 jungiklius (jungikliai nuo 1 iki 4) ir pasirinkite norimą žingsnį. Žingsnis, susietas su konkrečiu dešiniųjų jungiklių deriniu, bus rodomas septynių segmentų ekrane, o ekranas bus atnaujintas į naują susietą žingsnį, kai tik bus perjungti tinkami jungikliai. Poilsis gali būti priskirtas niekada nepriskiriant žingsnio vienam iš kairiųjų jungiklių arba pastabai priskiriant žingsnį, rodomą ekrane kaip 0. Suradę norimą žingsnį ir jis parodomas ekrane, paspauskite apatinį priskyrimo mygtuką, kad paskirstytumėte tą konkretų žingsnį pastabai.

3. Pakartokite 2 veiksmą trims likusioms natoms, atskirai įjungdami likusį kairįjį jungiklį, pasirinkdami atitinkamą žingsnį dešiniaisiais jungikliais ir paspausdami apatinį mygtuką, kad paskirstytumėte natą. Kelioms natoms gali būti priskirtas tas pats skambesys, vienu metu perkeliant daugiau nei vieną kairįjį jungiklį aukštyn.

4. Dabar, kai priskiriamos visos natų aikštelės, skaitmeninis sekos rinkiklis yra paruoštas groti. Norėdami paleisti garsiakalbio natas, tiesiog paspauskite dešinįjį paleidimo/pristabdymo mygtuką, kad pradėtumėte leisti muziką. Atkūrimo sekos tvarka atspindi su kairiuoju jungikliu susijusius žingsnius iš kairės į dešinę. Natos bus grojamos nustatytu smūgių per minutę skaičiumi 1, 2, 3, 4, 1, 2…. Ekrane bus rodoma pastaba, kuri šiuo metu grojama, kai garsiakalbiai leidžia muziką. Norėdami pristabdyti muzikos atkūrimą, tiesiog paspauskite dešinįjį mygtuką, tada muzika nustos groti ir ekrane bus rodomas pauzės simbolis. Dar kartą paspaudus dešinįjį mygtuką, atkūrimas bus atnaujintas.

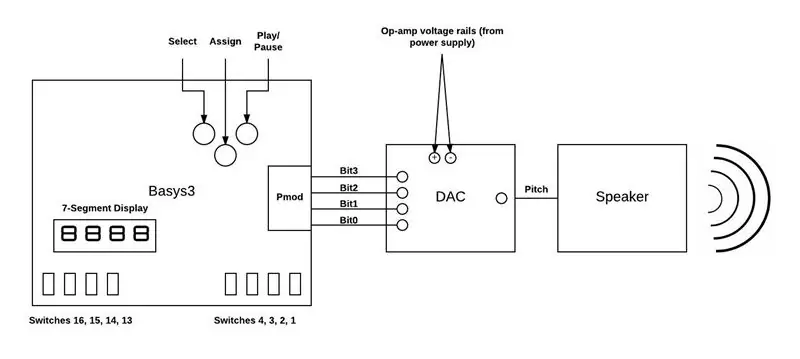

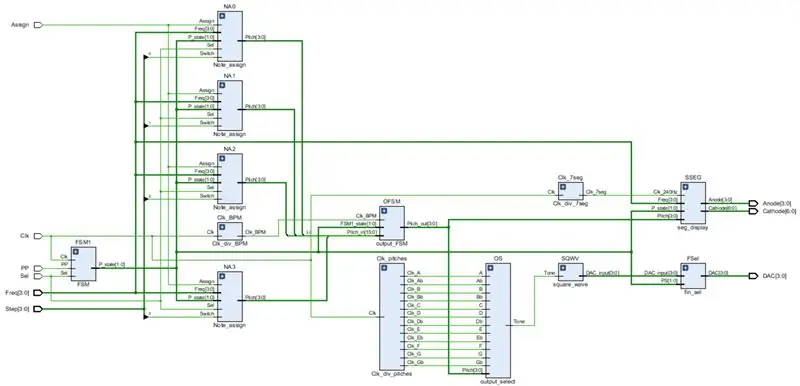

2 žingsnis: techninė informacija

Mūsų sintezatorius naudoja daugybę skirtingų skaitmeninių komponentų. Įtrauktos baigtinės būsenos mašinos, registrai, multiplekseriai, laikrodžio dalikliai ir dar daugiau. Norėdami sukurti savo sintezatorių, mes panaudojome 10 unikalių modulinių failų. Užuot padarę kiekvieną modulį komponentu, mes suskirstėme modulinius failus pagal funkcijas. Todėl dauguma modulių yra daugiau nei vienas komponentas. Atkreipkite dėmesį, kad aukščiau pateiktame paveikslėlyje parodyta, kad kiekvienas blokas yra susietas su mūsų geriausiu dizainu.

Mes aptarsime kiekvieną modulį, aprašydami įvestis ir išvestis, suskaidydami jo komponentus ir paaiškindami jo paskirtį bendrame projekte. Instrukcijos apačioje yra ZIP failas, kuriame yra kiekvienas projekte naudojamas VHDL kodo failas.

Įėjimai

- Clk (vietinis laikrodžio signalas)

- PP (paleisti/pristabdyti)

- Sel (įjunkite sintezatorių į pasirinkimo režimą)

- Priskirkite (priskirkite žingsnį žingsniui)

- Žingsnis (padėties užrašai)

- Dažnis (jungikliai, sukuriantys norimą žingsnį)

Išėjimai

- Anodas (7 segmentų anodai)

- Katodas (7 segmentų katodai)

- DAC (4 bitai, valdantys DAC)

3 žingsnis: techninė informacija

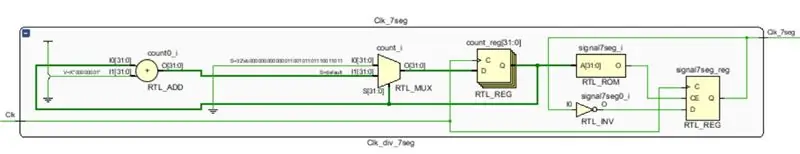

4 žingsnis: 7 segmentų laikrodžio daliklis

Mūsų sintezatorius naudoja tris laikrodžio daliklius, kurie visi gamina signalus, kurie mūsų projektui yra skirtingi. Laikrodžio daliklis priima laikrodžio signalą ir sukuria pakeistą signalą, kurio dažnis yra mažesnis už pradinį laikrodžio signalą. Pagrindinis „Basys 3“laikrodis yra 100 MHz. Tai dažnis, kurį naudoja mūsų laikrodžio dalikliai. Jei naudojate kitą FPGA plokštę su skirtingu laikrodžio dažniu, gali tekti pakeisti kodą.

7 segmentų laikrodžio daliklis sukuria signalą, kuris sukuria seg_display failą. Mes išsamiau paaiškinsime, kaip šis failas veikia, kai pateksime į jo skyrių. Iš esmės šis laikrodžio daliklis sukuria 240 Hz signalą, kuris bus naudojamas perjungti ekrane esančius anodus ir katodus. Signalas yra 240 Hz, nes dažnis, kuriuo žmogaus akis negali atpažinti šviesos nebuvimo, yra 60 Hz. Mes naudojame du skaitmenis, taigi, padvigubinus šį dažnį, kiekvienas skaitmuo svyruos 60 Hz dažniu. Tada padvigubiname, kad gautume 240 Hz, nes sistema keičiasi tik tada, kai signalas pakyla aukštai, o ne tada, kai sumažėja.

Norėdami tai pasiekti, skirstytuvas paima natūralų 100 MHz signalą ir skaičiuoja kiekvieną kylantį kraštą. Kai skaitiklis pasieks 416667, išvestis pereis nuo mažo iki aukšto arba atvirkščiai.

Įėjimai

Clk (vietinis laikrodžio signalas)

Išėjimai

Clk_7seg (į seg_display)

Komponentai

- D registras

- MUX

- Inverteris

- Sumažintojas

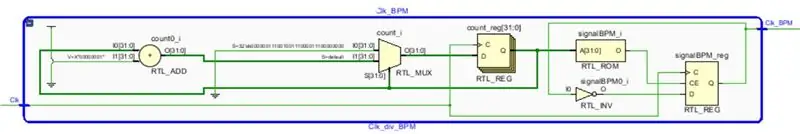

5 žingsnis: dūžių per minutę laikrodžio daliklis

BPM laikrodžio daliklis veikia panašiai. Šis skirstytuvas sukuria laikrodžio dažnį, kuris skatina perjungimą tarp keturių žingsnių, kai išleidžiami tonai atkūrimo būsenoje. Mes nusprendėme perjungti užrašus esant 100 BPM. Esant 100 BPM, kiekviena nata skambės 3/5 sekundės. Gauto signalo dažnis būtų 1,67 Hz.

Norėdami sukurti tokio dažnio signalą, mes vėl panaudojome skaičiavimo sistemą, tačiau šį kartą skaičius buvo 60 mln. Kiekvieną kartą, kai skaitiklis pasiekia 60 milijonų, išėjimo signalas perjungiamas aukštai arba žemai.

Įėjimai

Clk (natūralus laikrodžio dažnis)

Išėjimai

Clk_BPM (į išvesties_FSM)

Komponentai

- D registras

- MUX

- Inverteris

- Sumažintojas

6 žingsnis: Laikrodžio daliklis

„Pitches Clock Divider“yra didžiausias mūsų laikrodžio skirstytuvas. Šis daliklis išleidžia 12 skirtingų signalų, atitinkančių 12 skirtingų natų, kurias gali groti mūsų sintezatorius. Naudodamiesi pagrindinėmis muzikos teorijos žiniomis, mes padarėme išvadą, kad bitas ar autobusas gali svyruoti tokiu greičiu, kuris atitinka muzikos natų dažnį. Norėdami pamatyti mūsų naudojamus dažnius, žiūrėkite čia. Mes panaudojome ketvirtą aikštės oktavą.

Čia naudojama ta pati skaičiavimo sistema. Konkrečias vertes, į kurias skaičiavome, žr. Faile Clk_div_pitches.

Įėjimai

Clk (savitas laikrodžio dažnis)

Išėjimai

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (į išvesties pasirinkimą)

Komponentai

- D registras

- MUX

- Inverteris

- Sumažintojas

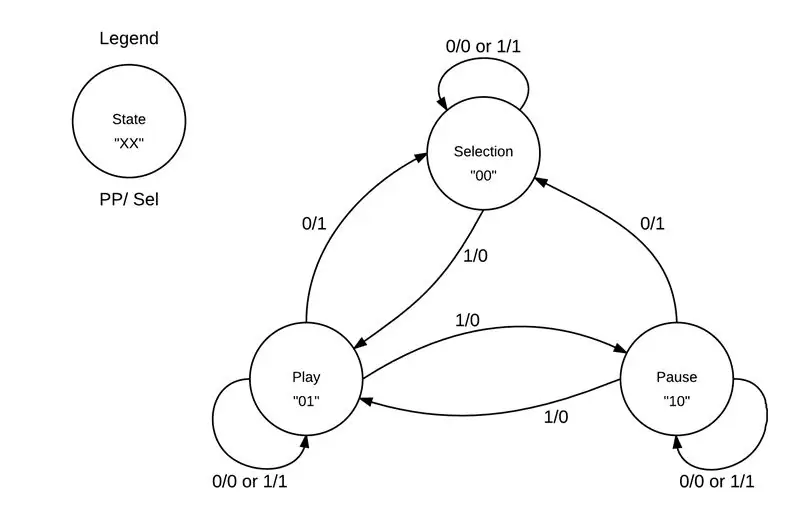

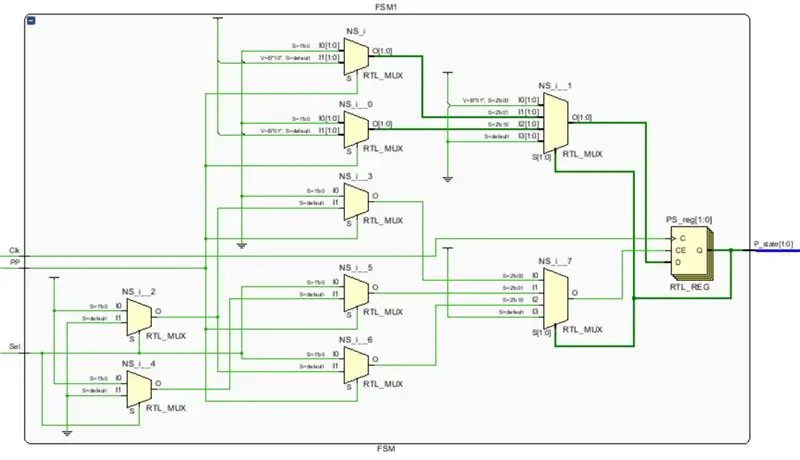

7 veiksmas: paleiskite/pristabdykite/pasirinkite būsenos mašiną

Mūsų projekte yra dvi baigtinės būsenos mašinos (FSM). FSM yra loginis įrenginys, galintis egzistuoti tik vienoje būsenoje iš riboto būsenų skaičiaus. Naudojant FSM, skaitmeninė grandinė gali pereiti į naują būseną, remiantis įvesties deriniu. Naudojant įvesties logiką, FSM būsena pasikeis, kai laikrodis pakils. Iš būsenos ir įėjimų į grandinę galite sukurti išvesties logiką, suteikiančią išvestis, kurios egzistuoja tik tuo atveju, jei MFV yra tam tikroje būsenoje.

PPS būsenos mašina yra pirmoji FSM mūsų grandinėje. Šiame MFV yra trys valstybės; Paleidimo, pristabdymo ir pasirinkimo režimai. Norėdami pereiti per skirtingas būsenas, naudojome PP ir pasirinkimo mygtukus. Žiūrėkite aukščiau esančią būsenų diagramą, kad sužinotumėte, kaip vyksta perėjimai tarp būsenų. Šį FSM perėjimą atlikome didėjančiame 100 MHz laikrodžio krašte, kad mašina negalėtų pereiti, kai paspaudžiamas vienas iš mygtukų, net ir labai trumpą laiką. Dabartinė būsena (P_state) yra vienintelė šio modulio išvestis.

Įėjimai

- Clk (savitas laikrodžio dažnis)

- Sel (kairysis mygtukas)

- PP (dešinysis mygtukas)

Išėjimai

P_state (dabartinė būsena, į output_FSM, note_assign, seg_dsiplay, final_select)

Komponentai

- MUX

- D registras

8 veiksmas: paleiskite/pristabdykite/pasirinkite būsenos mašiną

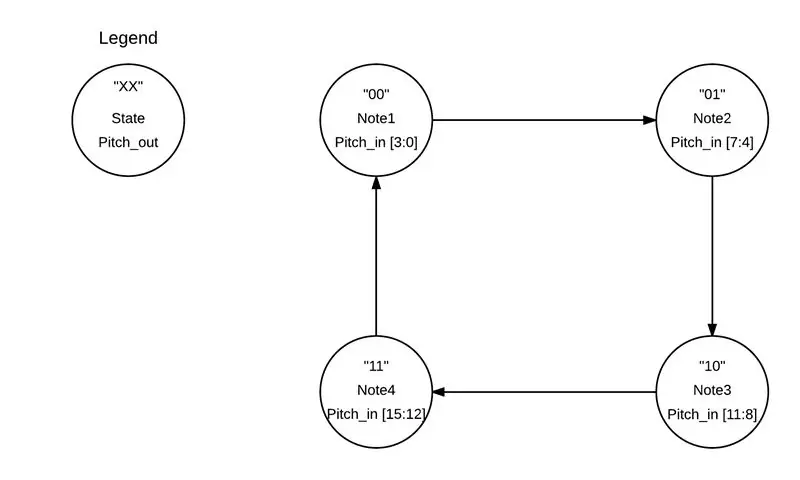

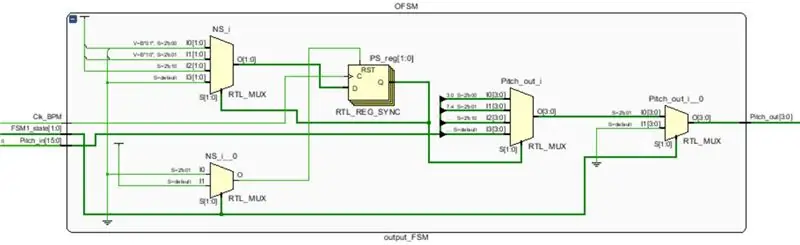

9 veiksmas: išveskite FSM

Tai antrasis ankstesniame skyriuje nurodytas MFV. Šis MFV atlieka kitokią funkciją nei kita, tačiau šio pagrindo esmė yra ta pati.

Išvesties FSM veikia tik tuo atveju, jei dabartinė pirmojo FSM būsena yra „01“(atkūrimo būsena). Iš esmės tai yra modulio įjungimas. Jei būsena yra „01“, FSM ketina perjungti būsenas BPM laikrodžio signalo kylančio krašto krašte. Mes tai darome, nes output_FSM kontroliuoja, kuris pasirinkto žingsnio dvejetainis skaičius bus siunčiamas į modulius output_select ir seg_display. FSM turi 16 bitų įvestį, gautą iš užrašų priskyrimo modulio, kuris bus aptariamas toliau. Išvesties_FSM būsenoje „00“modulis išves „xxxx“pirmajai priskirtajai pastabai. Tada „01“antrojoje natoje bus išvestas „yyyy“ir taip toliau kiekvienai natai prieš grįžtant prie pirmosios natos. Žr. Aukščiau esančią būsenos diagramą.

Šis FSM skiriasi nuo pirmojo, nes nėra įvesties logikos, leidžiančios valdyti perjungimą tarp būsenų. Vietoj to, FMV pradės veikti tik tada, kai būsena iš pirmojo MFV bus „01“, o tada ši FMV pereis tarp būsenų tik kylančiame laikrodžio signalo krašte. Kitas skirtumas yra tas, kad šis modulis turi išvesties logiką, tai reiškia, kad jis neišduoda dabartinės būsenos, o išleidžia dvejetainį skaičių, esantį toje būsenoje.

Įėjimai

- Clk_BPM (BPM laikrodžio signalas iš laikrodžio daliklio)

- FSM1_state (PS iš PPS FSM)

- „Pitch_in“(pastabos iš užrašų paskirstymo)

Išėjimai

„Pitch_out“(vienas žingsnis vienu metu, norint išvesti_pasirinkti ir seg_display)

Komponentai

- MUX

- D registras

10 veiksmas: išveskite FSM

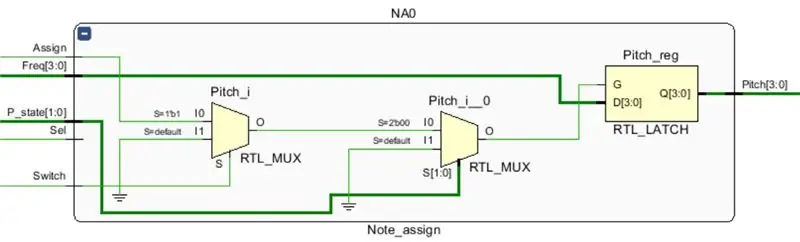

11 veiksmas: Pastaba Priskirti

Užrašų priskyrimo modulis yra atsakingas už faktinį žingsnio priskyrimą pozicinei natai ar žingsniui. Šis modulis iš tikrųjų yra gana paprastas. Pirmiausia ji patikrina, ar grandinė yra „pasirinkimo“būsenoje ir ar pakopinis jungiklis (toli kairėje) yra aukštas. Jei tai tiesa ir paspaudžiamas priskyrimo mygtukas, modulio išvestis bus lygi dvejetainiam skaičiui, kurį vaizduoja dažnio jungikliai (dešinėje).

Iš pradžių mes bandėme sukurti modulį, kuris iš tikrųjų išsaugotų vieną iš žingsnio laikrodžio signalų išvestyje, tačiau patyrėme problemų, kai išvestis pasikeitė, kad atitiktų įvesties laikrodžio signalus. Tai vienintelis modulis, daugiau nei vieną kartą naudojamas galutiniame projekte. Kiekviename žingsnyje yra susietas „note_assign“modulis, todėl kiekvienas modulio egzempliorius gauna vieną žingsnio magistralės bitą.

Įėjimai

- P_state (dabartinė būsena iš PPS FSM)

- Sel (kairysis mygtukas)

- Jungiklis (vieno žingsnio jungiklis)

- Dažnis (tolimieji dešinieji aukščio jungikliai)

- Priskirti (apatinis mygtukas, priskiriama pastaba)

Išėjimai

Pitch (dvejetainis skaičius, į output_FSM)

Komponentai

- MUX

- D užsiregistruok

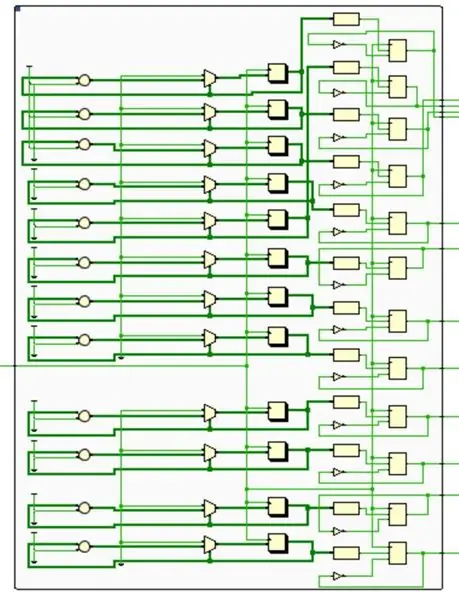

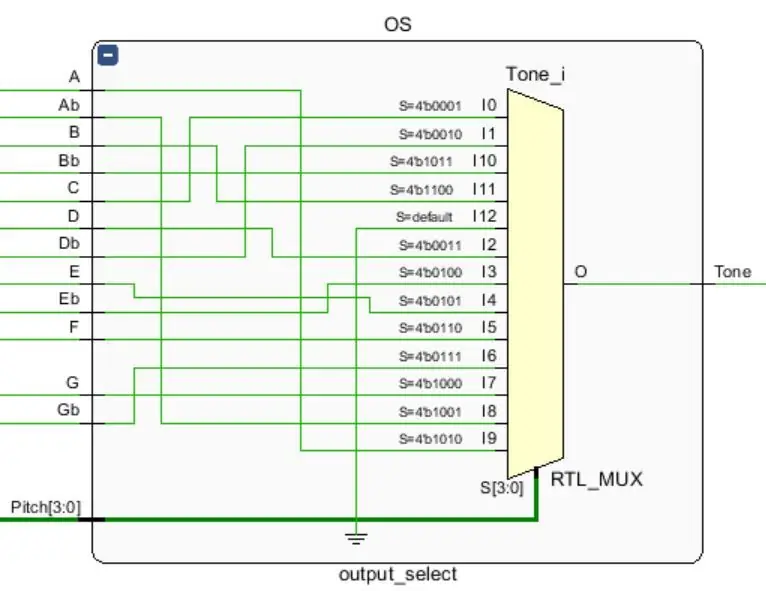

12 veiksmas: išvesties pasirinkimas

Išvesties pasirinkimas yra atsakingas už dvejetainio skaičiaus paėmimą ir jo prijungimą prie atitinkamo laikrodžio signalo. Nepaisant savo dydžio, tai taip pat yra gana paprastas modulis. „Output_select“iš esmės yra dvejetainis dekoderis, dekoduojantis žingsnio dvejetainį skaičių į konkretų laikrodžio signalą. Tiesą sakant, išvesties priskyrimas laikrodžio dažniui čia veikė geriau, palyginti su „Note_assign“moduliu, nes viskas, ką šis modulis turėjo padaryti, buvo MUX laikrodžio signalai su dvejetainiu skaičiumi, atitinkančiu valdymo įvestį.

Atsiprašome už keistą maršrutą, „Vivado“suskirstė „clk_div_pitches“failo garso signalus abėcėlės tvarka, tačiau šiam failai juos surinko didėjančiu dvejetainiu skaičiumi, todėl aikštelės buvo kitokia tvarka. Taip pat atkreipkite dėmesį, kad jei dvejetainis skaičius iš „output_FSM“buvo „0000“arba kas nors didesnis nei „1100“, tada MUX siunčiamas per plokščią „0“signalą.

Įvestis

- Pitch (iš output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (pikio laikrodžio signalai)

Išvestis

Tonas (vienas bitas, atitinkantis pasirinktą laikrodžio signalą, į square_wave)

Komponentai

MUX

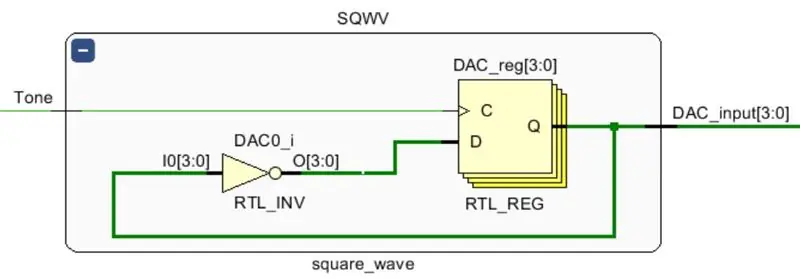

13 žingsnis: „Square Wave“gen

„Square_wave“modulis yra kvadratinės bangos generatorius, išvestas iš plokštės į DAC. Naudojant ankstesnio failo signalo signalą, ši kvadratinė banga apverčia 4 bitų skaičių tarp „0000“ir „1111“kylančiame tono krašte. Tonas yra specifinis garso dažnis, todėl „square_wave“sukuria skirtingo dažnio bangą, kai output_FSM pereina į kitą būseną. Šio modulio 4 bitų išvestis patenka į modulį „fin_sel“, kur logika nurodo, ar ši magistralė bus išvesta pagal būseną iš PPS FSM.

Šio kvadratinių bangų generatoriaus alternatyva yra sinusinės bangos sukūrimas. Nors tai greičiausiai suteiktų geresnį galutinį toną, jį įgyvendinti yra žymiai sunkiau, todėl nusprendėme tiesiog sugeneruoti kvadratinę bangą.

Įėjimai

Tonas (svyruojantis bitas iš output_select)

Išėjimai

DAC_input (svyruojanti 4 bitų magistralė, kuri keičiasi tuo pačiu dažnio tonu)

Komponentai

- Inverteris

- D registras

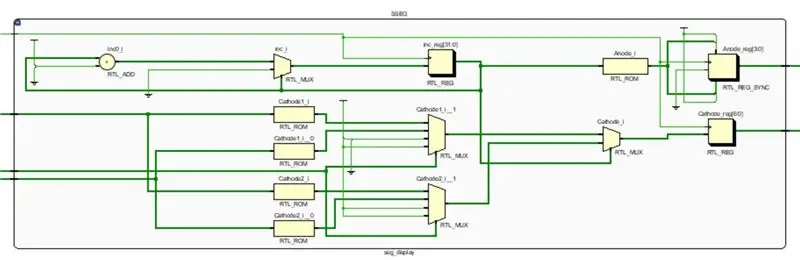

14 žingsnis: 7 segmentų ekranas

Modulis seg_display valdo 7 segmentų ekraną mūsų pagrindinėje plokštėje. Modulio viduje vyksta du procesai. Pirmasis procesas dekoduoja dažnį, kai jis yra „pasirinkimo“būsenoje, arba „Pitch“, kai yra „grojimo“režimas. „Pauzės“režimu modulis dekoduoja, kad būtų rodomas pauzės simbolis. Žvelgdami į VHDL kodą, galite pamatyti, kad dvejetainis dekoderis iš tikrųjų dekoduoja įvestį į du skirtingus signalus - katodą1 ir katodą2. Katodas1 reiškia raidę, atitinkančią rodomą žingsnį, o katodas2 - plokščią simbolį (b), jei toks yra. To priežastis yra antrasis „seg_display“modulio atliktas procesas.

„Basys3“plokštėje segmento ekranas turi bendrus katodus. Nors anodai valdo, kuris skaitmuo įjungtas, katodai kontroliuoja, kurie segmentai yra įjungti. Kadangi ekrane yra bendri katodai, tai reiškia, kad vienu metu galite rodyti tik vieną segmentų rinkinį. Tai kelia problemų šiam projektui, nes norime tuo pačiu metu rodyti raidę prie pirmojo skaitmens ir, jei reikia, plokščią simbolį. Dabar prisimeni 7seg laikrodžio signalą? Norėdami išspręsti šią problemą, mes keičiame anodus ir katodus pirmyn ir atgal pagal 7 segmento laikrodžio signalą. Kadangi laikrodžio signalas yra 240 Hz ir mes naudojame du skaitmenis, kiekvienas skaitmuo svyruoja 60 Hz dažniu. Žmogaus akiai atrodys, kad skaitmenys visai nesvyrauja.

Taip pat atkreipkite dėmesį, kad „basys3“plokštės ekrane naudojama neigiama logika. Tai reiškia, kad jei anodas arba katodas yra nustatytas į „0“, tas skaitmuo arba segmentas bus įjungtas ir atvirkščiai.

Įėjimai

- Pitch (dvejetainis užrašo numeris, naudojamas grojant)

- Dažnis (dažnio jungikliai, naudojami pasirinkimo būsenoje)

- P_state (dabartinė būsena iš PPS FSM)

- Clk_240Hz (laikrodžio signalas iš „Clk_div_7seg“, dvigubai 120, nes mes naudojame tik kylantį kraštą)

Išėjimai

- Katodas (magistralė, valdanti ekrano segmentus, galutinė išvestis)

- Anodas (magistralė, valdanti skaitmenis ekrane, galutinė išvestis)

Komponentai

- Fiksatorius

- MUX

- D registras

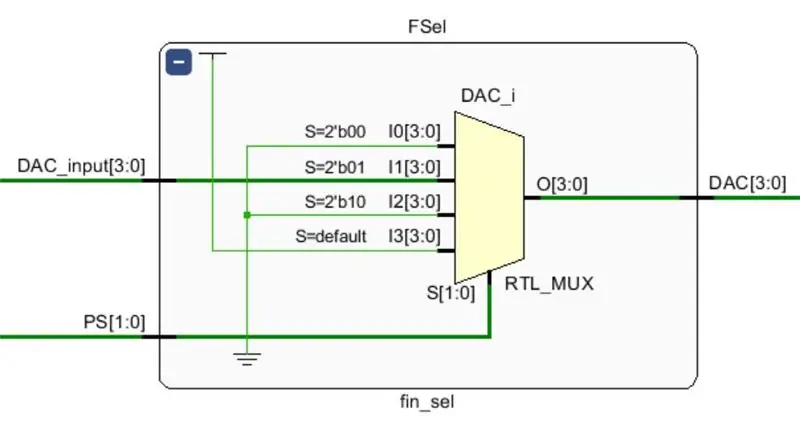

15 žingsnis: galutinis pasirinkimas

Galutinis pasirinkimas yra paskutinis šiame projekte naudojamas modulis. Kitas paprastas modulis, šis modulis valdo galutinę išvestį, kuri bus perduota DAC. Būdamas „pasirinkimo“arba „pristabdymo“būsenoje, modulis išves statinį „0000“, kad muzika nebūtų leidžiama iš garsiakalbių. „Paleidimo“būsenoje modulis išves svyruojančius 4 bitus, kaip nustatyta kvadratinėje bangoje.

Įėjimai

- P_state (dabartinė būsena iš PPS FSM)

- DAC_input (svyruojantis 4 bitų iš square_wave)

Išėjimai

DAC (lygus DAC_input žaidimo būsenoje, galutinė išvestis)

Komponentai

MUX

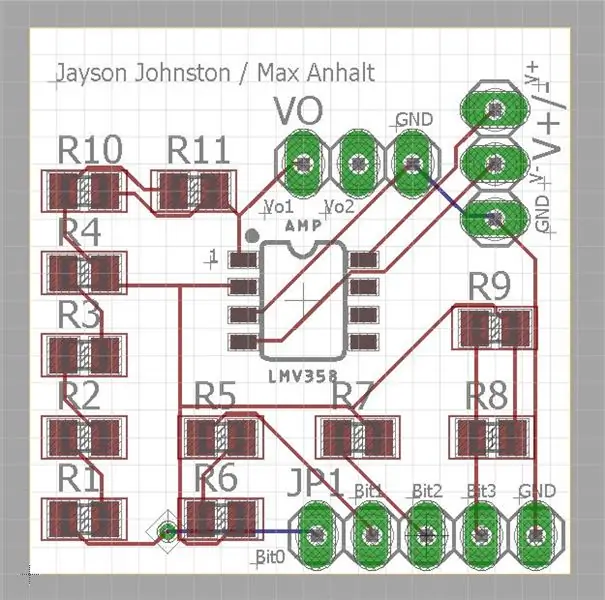

16 veiksmas: išoriniai įrenginiai: DAC

Skaitmeninis į analoginį keitiklis (DAC) priima diskretų signalą ir paverčia jį nuolatiniu signalu. Mūsų DAC turi keturis bitus ir yra pagamintas iš suminio stiprintuvo. Naudodami rezistorių santykį tiekimo ir grįžtamojo ryšio cikle, galėjome sukurti sistemą, kuri išvedama 16 skirtingų lygių, sukuriant „susumuojant“kiekvieną šaką. Bit0, viršutinė šaka, turi mažiausią svorį ir padidina mažiausią potencialą, kai yra didelis, dėl to šakos turi didesnį pasipriešinimą. Svoris didėja, kai einate žemyn šakomis. Jei skaičiuotumėte dvejetainiu būdu aukštyn ir atgal, naudodami bitų įvestis, išėjimo įtampa atrodytų kaip žingsnis po žingsnio sinusinė banga. Įvestis į DAC buvo prijungta prie vieno iš plokštės PMOD, kad būtų perduotas 4 bitų signalas.

DAC iš pradžių buvo surinktas elektrotechnikos klasei, jį suprojektavome ir litavome, o ne pirkome iš parduotuvės. Viršuje yra dizaino failo vaizdas, skirtas sukurti spausdintinę plokštę.

17 žingsnis: išoriniai įrenginiai: garsiakalbis

Šiam projektui nenorėsite nusipirkti super gražių garsiakalbių. Kaip jūs galite pasakyti, garsas yra gana paprastas. Mes nuėjome ir nusipirkome 8 USD kainuojantį kompiuterio garsiakalbių komplektą iš „Best Buy“. Viskas su ausinių lizdu veikia gerai. Monotoniškas taip pat veikia gerai. Jūs netgi galite naudoti ausines, bet galite jas išpūsti!

Norėdami prijungti DAC išvestį prie garsiakalbių, naudojome trumpiklius kabelius, tada išvesties kabelį laikėme prie ausinių lizdo galo ir įžeminimo kabelį prie pagrindo. Mes bandėme naudoti elektros juostą, kad laikytume kabelius, tačiau tai sukėlė daug trukdžių. Išbandžius kitokį juostos stilių, galima išspręsti šią problemą.

Kalbėdami apie garsiakalbius, pasukome juos į aukščiausią nustatymą ir girdėjome pakankamai stiprų triukšmą.

Ir tai yra paskutinis žingsnis kuriant skaitmeninį seką iš FPGA plokštės! Eikite į kitus du skyrius, kad atsisiųstumėte visą mūsų VHDL kodą ir pamatytumėte sekos veikimą.

18 veiksmas: vaizdo įrašo demonstracija

Šiame vaizdo įraše parodyta galutinė darbo projekto versija, įskaitant jungiklių priskyrimo 4 skirtingoms aikštelėms procesą ir garsiakalbius, grojančius atitinkamas natas.

19 veiksmas: VHDL kodas

Čia yra viso projekto kodas, įskaitant apribojimus ir sim failus, naudojamus kuriant seką. Atminkite, kad nepanaudoti dizaino failai tai sako architektūroje.

Rekomenduojamas:

„Arduino MIDI“ritmo sekos sekvenatorius: 8 žingsniai (su nuotraukomis)

„Arduino MIDI“ritmo sekcijų sekos davėjas: Turėti gerą programinės įrangos būgno aparatą šiandien yra paprasta ir pigu, tačiau naudojant pelę man smagu. Štai kodėl aš supratau, kas iš pradžių buvo skirta kaip grynas 64 žingsnių aparatūros MIDI būgnų sekos sekimo įrenginys, galintis suaktyvinti iki 12 skirtingų būgno elementų

Lygiagretus sekos sinchronizatorius: 17 žingsnių (su nuotraukomis)

Lygiagretus sekos sinchronizatorius: Tai vadovas, skirtas paprastam sekos kūrimui. Sekos sekimo įrenginys yra įrenginys, kuris cikliškai gamina veiksmus, kurie vėliau atlieka osciliatorių. Kiekvienas žingsnis gali būti priskirtas skirtingam tonui ir taip sukurti įdomias sekas ar garso efektus

Paprastas sekos nustatymas: 16 žingsnių (su nuotraukomis)

Paprastas sekvenatorius: Vienas iš geros muzikos kūrimo raktų yra beprasmis kartojimas. Būtent tai puikiai atlieka paprastas sekvenatorius. Tą patį daro vėl ir vėl aštuonių natų seka. Galite reguliuoti užrašo dažnumą, užrašo trukmę ir

Žvaigždžių takelis - „Arduino“varomas žvaigždžių rodyklė ir sekiklis: 11 žingsnių (su nuotraukomis)

Žvaigždžių takelis - „Arduino“varomas žvaigždžių rodyklė ir sekiklis: „Star track“yra „Arduino“pagrįsta „GoTo -mount“įkvėpta žvaigždžių sekimo sistema. Jis gali nukreipti ir sekti bet kurį dangaus objektą (įvestos dangaus koordinatės) su 2 „Arduinos“, giroskopu, RTC moduliu, dviem nebrangiais žingsniniais varikliais ir 3D spausdinta struktūra

Programuojamas RGB LED sekos nustatymo įrenginys (naudojant „Arduino“ir „Adafruit Trellis“): 7 žingsniai (su nuotraukomis)

Programuojamas RGB šviesos diodų sekos daviklis (naudojant „Arduino“ir „Adafruit Trellis“): mano sūnūs norėjo, kad jų staluose būtų apšviestos spalvotos LED juostos, o aš nenorėjau naudoti konservuoto RGB juostos valdiklio, nes žinojau, kad jiems nusibos fiksuoti modeliai. šie valdikliai turi. Taip pat pagalvojau, kad tai bus puiki proga sukurti