Turinys:

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:49.

- Paskutinį kartą keistas 2025-01-23 14:59.

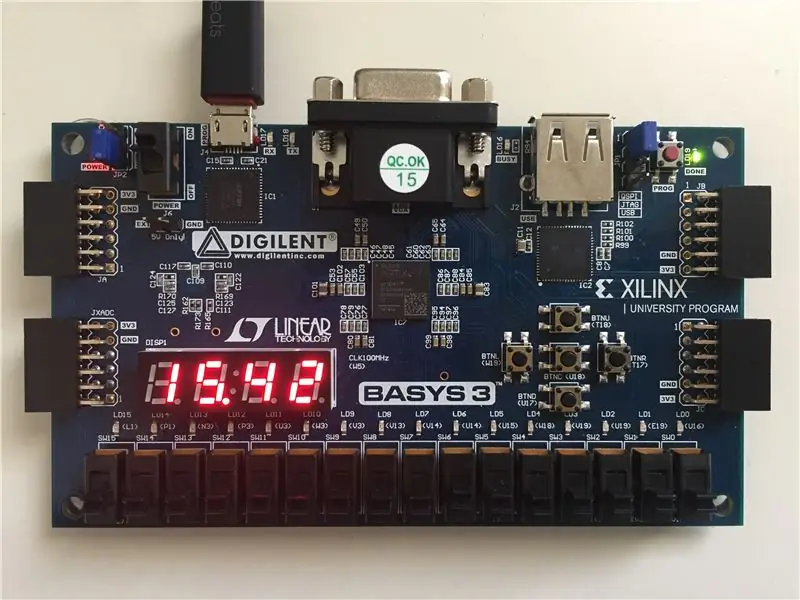

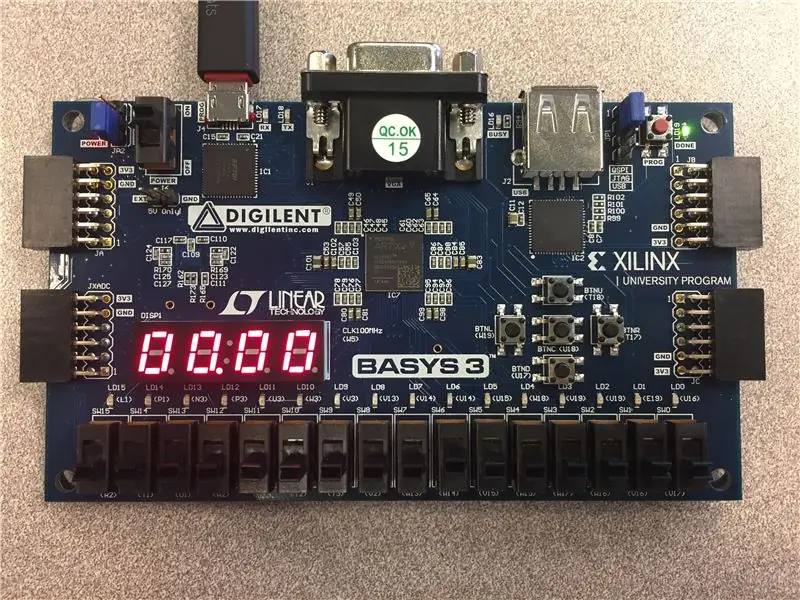

Tai yra pamoka, kaip padaryti chronometrą naudojant VHDL ir FPGA plokštę, pvz., „Basys3 Atrix-7“plokštę. Chronometras gali skaičiuoti nuo 00.00 sekundžių iki 99.99 sekundžių. Jame naudojami du mygtukai: vienas skirtas paleidimo/sustabdymo mygtukui, kitas - atstatymo mygtukui. Skaičiai rodomi lentos septynių segmentų ekrane, naudojant anodus ir katodus. Kad šis chronometras veiktų, reikia trijų skirtingų failų.

1 žingsnis: Aparatūra/programinė įranga

- „Basys3 Atrix-7“FPGA plokštė

- „Vivado Design Suite“iš „Xilinx“

- USB 2.0 A-„Micro-B“patinas

2 žingsnis: blokinė diagrama

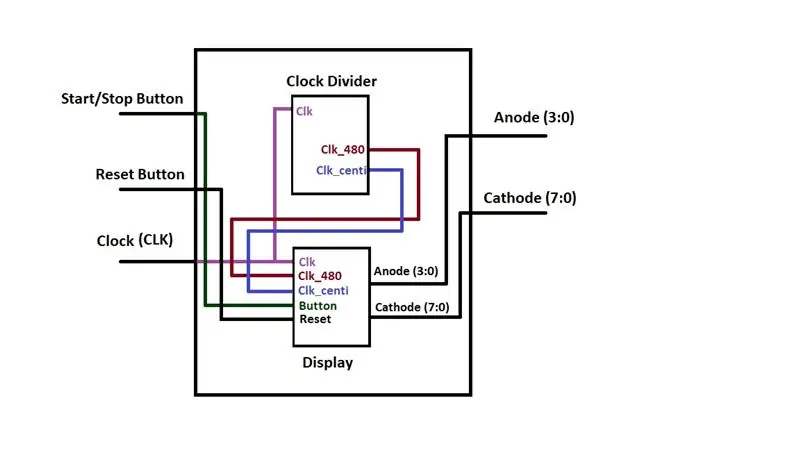

Bendras chronometras turi tris įėjimus ir du išėjimus. Trys įėjimai yra paleidimas/sustabdymas, atstatymas ir laikrodis. Pradėti/sustabdyti ir iš naujo nustatyti yra mygtukai, o laikrodis yra 100MHz plokštės laikrodis. Du išėjimai yra septynių segmentų ekrano anodai ir katodai.

Pirmasis modulis (laikrodžio daliklis) turi vieną įėjimą ir du išėjimus. Įvestis yra plokštės 100MHz laikrodis, o išėjimai yra du atskiri laikrodžiai, vienas veikia 480 Hz, o kitas - 0,5 MHz.

Antrasis modulis (ekranas) turi penkis įėjimus ir du išėjimus. Įvestys yra 100MHz plokštės laikrodis, du laikrodžiai iš laikrodžio daliklio modulio ir paleidimo/sustabdymo bei atstatymo mygtukai. Išėjimai yra anodai ir katodai.

Paskutinis modulis (modeliuojamas pagal visą blokinę schemą) turi tris įėjimus ir du išėjimus. Tai failas, kuris sujungia viską. Įvestys yra plokštės 100MHz ir paleidimo/sustabdymo bei atstatymo mygtukai. Išėjimai yra anodai ir katodai, valdantys septynių segmentų ekraną. Visi įėjimai ir išėjimai yra fiziškai ant galutinio modulio plokštės.

3 žingsnis: būsenos diagrama

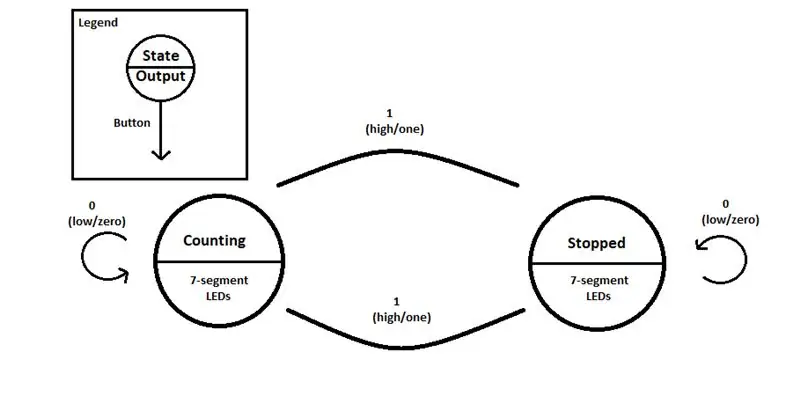

Aukščiau esančiame paveikslėlyje parodyta chronometro veikimo būsenos diagrama. Atstatymo mygtuko paspaudimas neturi jokios įtakos chronometro būklei. Kitą būseną nustato paleidimo/sustabdymo mygtukas. Paleidimas/sustabdymas yra „HIGH“, kai paspaudžiamas, bet ne tada, kai jis laikomas nuspaustas, ir „LOW“, kai mygtukas atsitraukia arba laikomas nuspaustas po to, kai akimirksniu yra „HIGH“.

Jei chronometras skaičiuoja ir paleidimo/sustabdymo mygtukas yra „HIGH“, jis nustoja skaičiuoti. Jei chronometras yra sustabdytas ir paleidimo/sustabdymo mygtukas yra „HIGH“, jis vėl pradeda skaičiuoti. Abiejose būsenose, jei paleidimo/sustabdymo mygtukas yra „LOW“, jis liks toje būsenoje, kurioje jis šiuo metu yra.

4 žingsnis: Laikrodžio daliklio modulis

Laikrodžio daliklio modulis turi vieną įvestį, 100MHz plokštės laikrodį ir du išėjimus - 480Hz ir 0,5MHz laikrodžius. 480 Hz laikrodis naudojamas visiems septynių segmentų ekrano šviesos diodams „įjungti“vienu metu, greitai perjungiant keturis. 0,5MHz laikrodis naudojamas, kad chronometras iš tikrųjų skaičiuotų centi sekundes.

5 žingsnis: Rodyti modulį

Šis ekrano modulis turi penkis įėjimus, plokštės 100MHz laikrodį, du laikrodžius iš laikrodžio modulio, paleidimo/sustabdymo ir atstatymo mygtukus bei du išėjimus - anodus ir katodus. Šis modulis taip pat turi „logiką“, kaip skaičiuojamas chronometras, ir jame yra baigtinės būsenos mašina.

6 žingsnis: Įrišimo modulis

Šis paskutinis modulis sujungia kitus du modulius. Jame yra trys įėjimai, 100MHz plokštės laikrodis ir paleidimo/sustabdymo bei atstatymo mygtukai bei du išėjimai - anodai ir katodai. 100MHz laikrodis eina į laikrodžio daliklio modulį ir ekrano modulį, o paleidimo/sustabdymo ir atstatymo mygtukai - į ekrano modulį. Laikrodžio daliklio modulio išėjimai (480Hz ir 0,5MHz) eina į du ekrano modulio laikrodžio įėjimus. Rodymo modulio išėjimai (anodai ir katodai) patenka į galutinio modulio išėjimus.

7 žingsnis: Apribojimai

Du įėjimai gali būti bet kokie „Basys3 Atrix-7“FPGA plokštės mygtukai, o išėjimai bus keturi anodai ir aštuoni katodai (nes taip pat norite dešimtainio taško tarp sekundžių ir milisekundžių) septynių segmentų ekrane.

8 žingsnis: padaryta

Įkelkite programą į „Basys3 Atrix-7 FPGA Board“ir paspauskite pradžios/sustabdymo mygtuką, kad chronometras veiktų!

Rekomenduojamas:

Pagrindinis chronometras naudojant VHDL ir „Basys3 Board“: 9 žingsniai

Pagrindinis chronometras naudojant VHDL ir „Basys3 Board“: Sveiki atvykę į instrukcijas, kaip sukurti chronometrą naudojant pagrindinę VHDL ir „Basys 3“plokštę. Džiaugiamės galėdami pasidalinti savo projektu su jumis! Tai buvo paskutinis CPE 133 (skaitmeninio dizaino) kurso projektas Cal Poly, SLO 2016 m. Rudenį. Projektas, kurį mes kuriame

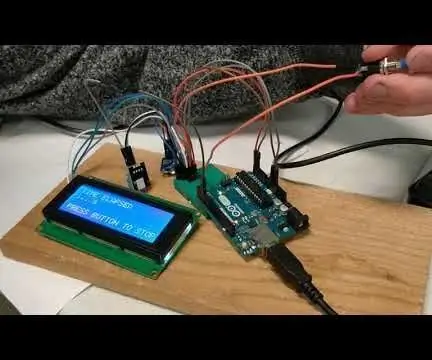

„Arduino“chronometras: 4 žingsniai (su nuotraukomis)

„Arduino“chronometras: ši instrukcija parodys, kaip iš „Arduino“padaryti laikrodį

Paprastas „Arduino“laikrodis / chronometras: 6 žingsniai (su nuotraukomis)

Paprastas „Arduino“laikrodis / chronometras: šis " nurodomas " parodys ir išmokys jus padaryti paprastą „Arduino Uno“laikrodį, kuris taip pat veikia kaip chronometras vos keliais paprastais veiksmais

Chronometras 30 m bėgimui („Arduino“): 6 žingsniai (su nuotraukomis)

Chronometras 30 m bėgimui („Arduino“): Šis projektas buvo sukurtas konkrečiam tikslui Suomijos beisbolo treniruotėse ir tikrinant jaunesnių žaidėjų greitį 30 m bėgime. Šis arduino projektas taip pat buvo mano studijų kursinis projektas. Projektas turėjo tam tikrų pakilimų ir nuosmukių, bet dabar bent jau tai veikia

VHDL vienos minutės chronometras: 5 žingsniai

VHDL vienos minutės chronometras: tai pamoka, kaip sukurti vienos minutės chronometrą naudojant VHDL ir „Basys 3“plokštę. Toks įrenginys idealiai tinka žaidimams, kuriuose kiekvienas žaidėjas turi daugiausiai vienos minutės savo judesiui atlikti. Chronometras tiksliai rodo sekundes ir milisekundes