Turinys:

- Prekės

- 1 veiksmas: nuoseklaus prievado reikalavimai

- 2 žingsnis: PIC programavimo reikalavimai

- 3 žingsnis: JDM specifikacija

- 4 žingsnis: grandinės aprašymas

- 5 žingsnis: pasiruoškite modeliavimui

- 6 žingsnis: ICSP pakeitimai

- 7 žingsnis: modeliavimo rezultatai

- 8 žingsnis: Išvados

- 9 žingsnis: ir pagaliau

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:44.

- Paskutinį kartą keistas 2025-06-01 06:09.

JDM yra populiarus PIC programuotojas, nes naudoja nuoseklųjį prievadą, minimalų komponentų skaičių ir nereikalauja maitinimo. Tačiau ten yra painiavos, kai internete yra daug programuotojų variantų, kurie iš jų dirba su kokiais PIC? Šioje „pamokomoje“mes išbandėme JDM ir aš parodau, kaip imituoti grandinę naudojant „Spice“, kuri atsakys į visus jūsų klausimus!

Prekės

„LTspice“, kurią galite atsisiųsti iš analoginių įrenginių čia.

Čia taip pat reikia JDM grandinės failų.

1 veiksmas: nuoseklaus prievado reikalavimai

JDM reikalingas nuoseklusis prievadas, atitinkantis EIA232 specifikacijas, idealiu atveju su +12/-12 įtampos lygiais.

Pagal „Texas Instruments Line Driver MC1488“duomenų lapą (3 pav.)

Išėjimo varža = 4V/8mA = 500 omų.

Trumpojo jungimo srovės riba = 12 mV, be laiko apribojimo - nepažeista lustas.

Rekomenduojama linijinio imtuvo įėjimo varža = 3-7 k.

Senesnių stalinių kompiuterių nuoseklieji prievadai naudoja +12v/-12V, atitinkančius šį reikalavimą.

Naujesnių nešiojamųjų kompiuterių nuoseklieji prievadai naudoja žemesnę įtampą. JDM gali veikti arba ne, atsakymas yra sudėtingesnis.

2 žingsnis: PIC programavimo reikalavimai

Informacija apie PIC programavimo reikalavimus gaunama iš „Microchip“. Aukščiau aprašytas tipiškas įrenginys.

3 žingsnis: JDM specifikacija

Ar pradinė JDM svetainė buvo prarasta laikui bėgant? Tai leidžia mums atspėti, ką dizaineris iš pradžių numatė specifikacijai.

- Pateikite VDD = 5V ir ne daugiau kaip IDD = 2mA („lizdo“versijoje)

- Pateikite VHH = 13V ir ne daugiau kaip IHH = 0,2 mA.

- MCLR Pakilimo laikas tVHHR = maks. 1uS.

- ICSP versija turi sugebėti pritraukti žemą MCLR prieš 22k traukimą į taikinį.

4 žingsnis: grandinės aprašymas

Paveikslas JDM1 yra pagrįstas „standartine“JDM grandine, paimta iš PICPgm svetainės. Tai yra „PIC in Socket“programuotojas, kuriame PIC gauna energiją iš TX ir RTS kaiščių. Pradinę diagramą buvo sunku suprasti, todėl ją perpiešiau naudodamas įprastą srovės tekėjimo iš viršaus į apačią konvenciją. Pridėjau LED indikatorius „RESET“, „PROG“ir „RTS“, kurie yra būtini statybos ir bandymų metu. Tikimės, kad tai neturės jokio žalingo poveikio elgesiui.

Įprasta grandinės projektavimo sutartis yra bendra visiems pagrindams, tačiau pagrindinis JDM bruožas yra tas, kad nuosekliojo prievado įžeminimas (GND) yra prijungtas prie VDD. Tai sukelia painiavą, nes nuosekliojo prievado signalai matuojami atsižvelgiant į GND, PIC signalus į loginį įžeminimą (VSS).

Kai TX padidėja, Q1 elgiasi kaip du į priekį nukreipti diodai. (Q1 kolektorius nėra atvirkštinis, kaip įprastai veikiant tranzistoriui). Q1 kolektorius įkrauna C2, kurį Zener (D3) užspaudžia VDD+8V. Q1 emitteris tiekia 13V į MCLR programavimo/tikrinimo režimui.

Kai TX sumažėja, kondensatorius C3 įkraunamas per D1, o VSS Zener (D5) pritvirtina prie VDD-5V. Taip pat TX fiksuojamas (VSS-0.6) D1. Q1 išjungtas, C1 pasilieka mokestį už kitą programavimo impulsą. D2 MCLR įtvirtina esant 0 V įtampai, todėl PIC dabar nustatytas iš naujo.

Kai RTS yra didelis, laikrodis perduodamas PGC. D4 spaustukas PGC esant aukštai VDD logikai. Kai RTS yra žemas, kondensatorius C3 įkraunamas per D6, o VSS ZDER (D5) pritvirtina prie VDD-5V. D6 fiksuoja PGC prie VSS arba logikos 0.

Programavimo metu DTR siunčiami duomenys nuskaitomi PGD, kurį PIC sukonfigūruoja kaip įvestį. Kai DTR yra didelis, Q2 veikia kaip „emiterio sekėjas“, o PGD įtampa yra maždaug (VDD-0,6) arba logika 1. Kai DTR yra žemas, Q2 veikia kaip blogas tranzistorius (emiterio ir kolektoriaus kaiščiai apversti). Q2 žemina PGD, kurį VSS arba logika 0 fiksuoja D7.

Patikrinimo metu PIC sukonfigūruoja PGD kaip išvestį duomenims siųsti į nuoseklųjį prievadą. DTR turi būti nustatytas aukštas, o duomenys skaitomi naudojant CTS. Kai PGD išėjimas yra didelis, Q2 yra išjungtas, CTS = DTR = +12V. Kai PGD išvestis yra maža, Q2 įjungtas. Q2 kolektorius traukia srovę (12V+5V)/(1k+1k5) = 7mA iš DTR ir traukia žemą CTS iki VSS.

5 žingsnis: pasiruoškite modeliavimui

Atsisiųskite „LT spice“, išsaugokite ir atidarykite čia pateiktus grandinės failus (*.asc). Norėdami imituoti grandinę, turime jai duoti keletą įėjimų, tada „atsekti“išėjimus. V1, V2 V3 imituoja 12 V nuoseklųjį prievadą su išėjimo varža R11, R12, R13.

- V1 generuoja 2 programos impulsus TX nuo 0,5 ms iki 4,5 ms

- V2 generuoja duomenų impulsų srautą DTR nuo 1,5 iki 4,5 ms

- V3 generuoja laikrodžio impulsų pliūpsnį RTS nuo 0,5 iki 3,5 ms

Visi komponentai V4, X1, R15 ir R16 yra modeliavimo dalis.

- V4 generuoja 2 impulsus nuo 2,5 iki 4,5 ms, kad patikrintų duomenis.

- „Jumper X1“imituoja PGD išvestį.

- R15, R16 imituoja PIC „įkėlimą“į VDD ir MCLR.

6 žingsnis: ICSP pakeitimai

JDM3 paveiksle parodyta „grandinės“programavimo versija. Pakeitimai iš originalo yra

- Pakeiskite ZIF lizdą ICSP jungtimi.

- PIC dabar maitinamas maitinimu į tikslinę grandinę (V5).

- Nuimkite 5V „Zener“(D5).

- Mažas 100pF kondensatorius (C4) yra perkeltas šalia PIC tikslinėje grandinėje.

- Šviesos diodai, jei įmanoma, ima maitinimą iš plokštės.

- Tikslinėje grandinėje reikalingi MCLR traukiamasis rezistorius (R10) ir diodas (D10).

- ĮSPĖJIMAS. Tikslinėje plokštėje turi būti „plaukiojantis“maitinimas, idealiu atveju - baterija.

- Nejunkite tikslinio įžeminimo (VSS) prie kompiuterio/kompiuterio įžeminimo prijungdami bet kokius kitus kompiuterio prievadus tuo pačiu metu kaip ir JDM.

Imitavus JDM1, paaiškėjo ilgo C2 įkrovimo laiko problema. Tada, perskaičius „Fruttenboel“, atrodo, kad C2 ir Q1 buvo pridėti kaip originalas. Aš negaliu galvoti, ką C2 ir Q1 ketina daryti, be problemų. Taigi, kalbant apie „JDM4“, grįžtame prie senesnio „Fruttenboel“dizaino, kuris yra paprastas ir suprantamas. D1 ir D3/LED2 spaustukas MCLR tarp VSS ir VDD+8V. R1 vertė sumažinta iki 3 k3, to pakanka, kad LED2 apšviestų esant 12 V įtampai.

JDM4 taip pat sukurtas dirbti su silpnesniais nuosekliais prievadais. Kai TX yra didelis (+9V), TX srovės šaltinis = (9-8)/(1k +3k3) = 0,2ma, to pakanka, kad MCLR būtų aukštas, nors ir nepakankamas šviesos diodui2. Kai TX sumažėja (apie -7V), TX srovė krinta = (9-7)/1k = 2mA. LED1 srovė = (7-2 LED)/(2k7) = 1,8 mA. MCLR nusileidimo srovė = 7-5,5/3k3 = 0,5 mA.

Ši grandinė taip pat buvo išbandyta (JDM5 modeliavimas), siekiant išsiaiškinti, kas atsitinka su mažiausiai +/- 7V nuosekliais prievadais, kai nepakanka įtampos palaikyti VHH = 13V. Dabar paaiškėja C1 paskirtis, C1 sukuria trumpą ir padidintą MCLR, 33us smaigalį ant kylančio TX krašto, pakankamai ilgo, kad PIC galėtų įjungti programavimo režimą? Bet nuimkite trumpiklį X2 (išjunkite LED1), nes nepakanka srovės, kad būtų galima pritraukti žemą MCLR ir kartu apšviesti LED1. Kai TX sumažėja, TX srovės kriauklė = (7V-5,5 V)/(1k+3k3) = 0,3 mA, to pakanka, kad MCLR būtų žemas prieš pritraukiantį R10.

7 žingsnis: modeliavimo rezultatai

Norėdami peržiūrėti grafinius failus, geriau dešiniuoju pelės mygtuku spustelėkite žemiau esančias nuorodas, tada pasirinkite „Atidaryti nuorodą naujame skirtuke“

1 modeliavimas: MCLR, VSS ir RTS pėdsakai originaliam JDM1. Iš karto pastebimi 1, 2 ir 3 pastebėjimai.

2 modeliavimas: MCLR ir VSS bei modifikuoto JDM2 RTS pėdsakas, kuris išsprendžia ankstesnes problemas.

3 modeliavimas: PGD, VSS ir PGC pėdsakai JDM2 siunčiant duomenis programos režimu. 4 stebėjimas esant 3,5 mS.

4 modeliavimas: PGD, VSS ir CTS pėdsakai JDM2 tikrinimo režimu (įdėtas trumpiklis X1). Gerai

5 modeliavimas: JDM3 MCLR, VSS, PGD ir PGC pėdsakai. ICSP, naudojant grandinės galią, išsprendžia daugybę problemų.

6 modeliavimas: MCLR, VSS, PGD ir PGC pėdsakai JDM4 su +/- 9V nuosekliu prievadu. MCLR iš karto pakyla, visiškai veikia.

7 modeliavimas: MCLR, VSS ir TX pėdsakai JDM5 su +/- 7V nuosekliu prievadu ir trumpikliu X2. C1 sukuria +ve padidėjimą (smaigalį) kylančiame MCLR krašte, beveik tiek, kad pakeltų MCLR virš TX iki 13 V.

8 žingsnis: Išvados

„Spice“tikrai gerai atskleidžia grandinės veikimo „paslėptas paslaptis“. Akivaizdu, kad JDM grandinė veikia ir yra suderinama su daugeliu PIC mikroschemų, tačiau šie pastebėjimai atskleidžia galimus apribojimus/suderinamumo problemas/gedimus?

- Ilgas MCLR kilimo laikas, o C2 įkraunamas į VPP pirmą TX impulsą. Neatitinka specifikacijos 3.

- Serijinis prievadas įkrauna C2, kai TX yra didelis, o RTS - žemas. Tačiau RTS taip pat turi įkrauti C3. Kai abu įvyksta vienu metu, tai padidina RTS apkrovą, todėl C3 ima įkrovą (VSS pakyla) 2 ms imitacijos metu. Neatitinka specifikacijos 1.

- C3 praranda įkrovą (VSS pradeda kilti), kai laikrodžio impulsai sustoja ties 3,5 ms.

- Koks yra C2 tikslas, ar jis apskritai reikalingas?

Sprendimai

- Tikėtina, kad „PICPgm“naudoja programinę įrangą „darbo ratas“. Jis turi taikyti ilgą TX impulsą iš anksto įkrauti C2, tada įjungti programavimo režimą tik po antrojo TX impulso? Modeliavimui aš sumažinau C2 vertę iki 1uF, kad kilimo laikas būtų 1 ms. Ne idealus sprendimas.

- Padalinkite C2 ir C3, kad jie įkrautų nepriklausomai. Vienas nedidelis JDM2, C2 pakeitimas yra nurodytas GND, o ne VSS.

- Išsprendė JDM3. ICSP yra daug patikimesnis, nes PIC maitinamas tiksline grandine.

- JDM4 išsprendžia 1 problemą. Tai paprasta konstrukcija, visiškai pašalinanti C2.

9 žingsnis: ir pagaliau

Pudingo įrodymas yra valgymas. Šis JDM veikia, todėl ir toliau jį naudokite.

Ir mano rekomendacijos yra šios:

- naudoti JDM2 programuojant lizdus ir 12V nuoseklius prievadus,

- naudokite JDM4 ICSP programuotojui ir nuosekliam prievadui, viršijančiam +/- 9V,

- naudokite JDM4 su pašalintu jungikliu X2, jei serijiniai prievadai viršija +/- 7V.

Nuorodos:

„Analog Devices LT“prieskonis

picpgm

Fruttenboel

Sekite daugiau PIC projektų „Sly-corner“

Rekomenduojamas:

„Elegoo Super Started Kit Uno R3“apžvalga: 4 žingsniai

„Elegoo Super Started Kit Uno R3“apžvalga: Prieš kelias dienas „Elegoo“atsiuntė man šį „Super Starter Kit“testavimui. Taigi, pažiūrėkime, kas yra viduje. Atidarę šį kompaktišką dėklą, galime pamatyti daug dalykų. Viršelyje yra rodyklė su visais komponentais. Viduje turime padėkos atviruką su visomis

„KS-Garden“: apžvalga: 9 žingsniai

„KS-Garden“: apžvalga: „KS-Garden“gali būti naudojamas drėkinimui/vėdinimui. sistemos dėžutė - „Relais“ir maitinimo blokas

ESP -01 programuotojo nulaužimas - lengvas :): 6 žingsniai

ESP-01 programuotojo nulaužimas-lengvasis :): Sveiki, ESPers, šioje pamokoje aš jums parodysiu paprastą įsilaužimą, kad sukurtumėte programuotoją ESP-01 / ESP8266-01 / ES-01 moduliui. Daugelis iš mūsų naudojo „Arduino“plokštę arba FTDI USB-TTL įrenginius kaip šio modulio programuotojus. Abu metodai veikia gerai. Bet t

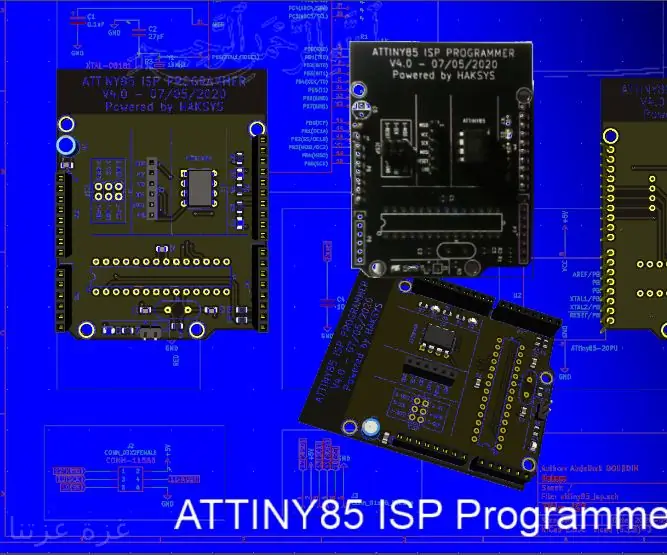

Dar vienas ATTINY85 ISP programuotojo skydas „Arduino“: 8 žingsniai

Dar vienas „ATTINY85“ISP programuotojo skydas „Arduino“: Atnaujintas Interneto svetainė „ATTINY85“programuotojo skydas skirtas lengvai programuoti ATTiny85 µ valdiklius. Skydas turi būti prijungtas prie „Arduino Uno“plokštės. „Arduino Uno“yra paruoštas veikti Serijinis programuotojas & quot

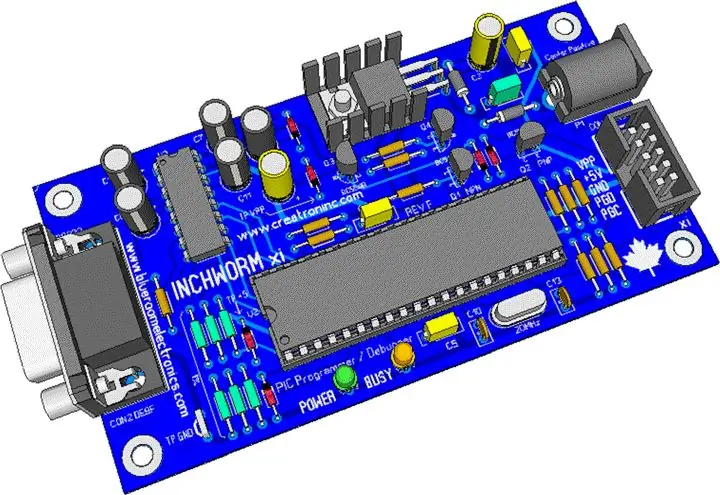

„Inchworm ICD2“PIC programuotojo / derintojo kūrimas: 7 žingsniai

„Inchworm ICD2“PIC programuotojo / derintojo kūrimas: šis nurodymas yra iliustruotas žingsnis kuriant ICD2 kloną, vadinamą „Inchworm“. Tai tiesioginis rinkinys, leidžiantis sukurti su MPLAB ICD2 suderinamą programuotoją ir derintoją. Yra daug programuotojų, bet labai nedaugelis apima