Turinys:

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:45.

- Paskutinį kartą keistas 2025-01-23 14:59.

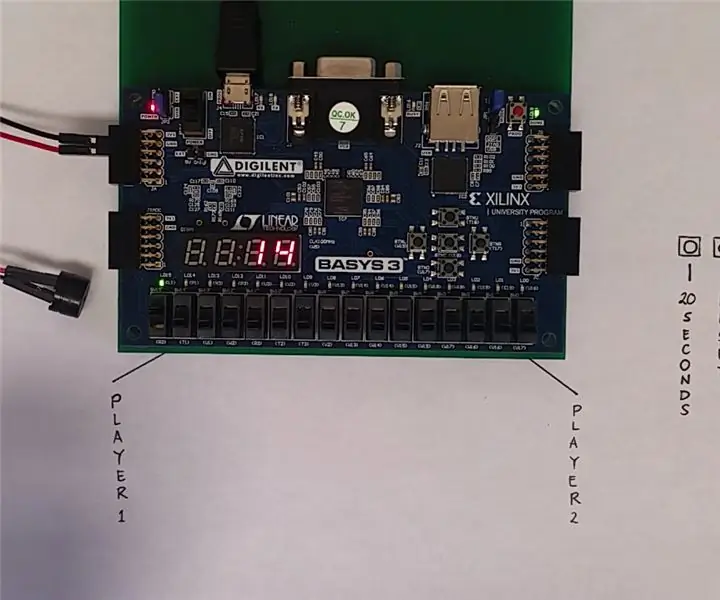

Šiame projekte sukurta konkurencinga garso signalų sistema veikia panašiai kaip regioninėse ir nacionalinėse mokslo taurės varžybose naudojamos garsinių signalų sistemos. Šį projektą įkvėpė trejų metų dalyvavimas gimnazijos mokslo dubenėlio komandoje. Mes visada norėjome atkurti užrakinimo signalų sistemą su 5 ir 20 sekundžių laikmačiu.

Norėdami sužinoti apie garso signalų sistemą, mokslo dubenėlio garsiniai signalai yra užprogramuoti įvesti ne daugiau kaip 8 žaidėjus (su 8 atskirais garsiniais signalais). Paspaudus vieną garsinį signalą, užsidegs pirmojo žmogaus garsinis signalas, nurodantis, kuris žaidėjas gauna klausimą. Likę žaidėjai bus „užrakinti“, o tai reiškia, kad jų garsiniai signalai nereaguos, kol moderatorius nenustatys signalų sistemos.

Kai moderatorius perskaitys klausimus, jis paspaus mygtuką, kad paleistų atgalinės atskaitos laikmatį, kuris bus rodomas septynių segmentų ekrane. Po „išmetimo“klausimo moderatorius gali paspausti dešinįjį mygtuką ir pradėti skaičiuoti nuo 5 sekundžių. Tuo tarpu po „premijos“klausimo moderatorius gali paspausti kairįjį mygtuką ir pradėti skaičiuoti nuo 20 sekundžių. Kai laikmatis pasieks nulį, garso signalizatorius parodys, kad grotuvui pritrūko laiko.

Norėdami iš naujo nustatyti sistemą ir atgalinės atskaitos laikmatį, moderatorius gali paspausti centrinį mygtuką. Norėdami iš naujo nustatyti blokavimo mechanizmą ir grotuvo šviesos diodus, 1 ir 2 grotuvo jungikliai turi būti žemai.

1 žingsnis: medžiagos

Jums reikės:

- „Basys3“plokštė (arba lygiavertė FPGA plokštė)

- „Micro-B“USB kabelis

- Garsiakalbis (naudojau pasyvų garsiakalbį)

- 2 laidai

- Programinė įranga, kurią reikia įdiegti FPGA (aš naudojau „Vivado“)

- Konkurencinės garsinės sistemos failas

2 žingsnis: juodosios dėžės diagrama

Juodosios dėžės schema rodo įėjimus ir išėjimus, kurie bus naudojami šioje signalų sistemoje.

ĮVEDIMAI:

player1, player2 Šie įėjimai yra prijungti prie dviejų „Basys3“plokštės jungiklių. Patogumui bus naudojami kairieji ir dešinieji jungikliai.

atstatymas Centrinis mygtukas bus naudojamas atstatyti mygtuką.

count_down_20_sec Kairysis mygtukas bus naudojamas kaip 20 sekundžių laikmačio mygtukas.

count_down_5_sec Dešinysis mygtukas bus naudojamas 20 sekundžių laikmačio mygtukui pavaizduoti. Kad 20 ir 5 sekundžių laikmatis įsijungtų, laikykite nuspaudę mygtuką, kol septynių segmentų ekrane pasirodys laikmatis.

CLK FPGA plokštė sukurs laikrodį, kuris veikia 10 ns dažniu.

Išėjimai:

garsiakalbis Garsiakalbio išvestis prijungta prie išorinio garsinio signalo arba garsiakalbio. Garsiakalbį turėsite prijungti prie „Basys3“plokštės JA pmod prievadų. Šis žingsnis bus aprašytas toliau.

speaker_LED Ši išvestis yra prijungta prie plokštės centre esančio šviesos diodo ir tik parodys, kada FPGA garsiakalbio išvestis yra didelė. Tai galite naudoti išbandydami išorinį garsiakalbį. Atminkite, kad kai kurie „pmod“prievadai gali neveikti gerai, todėl galite išbandyti skirtingus ir naudoti šviesos diodą, kad patikrintumėte, ar garsiakalbis turi būti įjungtas.

SEGMENTAI Ši išvestis yra prijungta prie aštuonių atskirų segmentų septynių segmentų ekrane, įskaitant dešimtainį tašką.

DISP_LT Ši išvestis yra prijungta prie keturių septynių segmentų ekrano anodų.

player_LED Šis išėjimas yra 2 paketų signalas, prijungtas prie šviesos diodų, esančių virš grotuvo1 ir grotuvo2 jungiklių. Pirmasis žaidėjas, pasukęs atitinkamą jungiklį, bus rodomas šviesos diodu. Atminkite, kad abu šviesos diodai negali degti vienu metu.

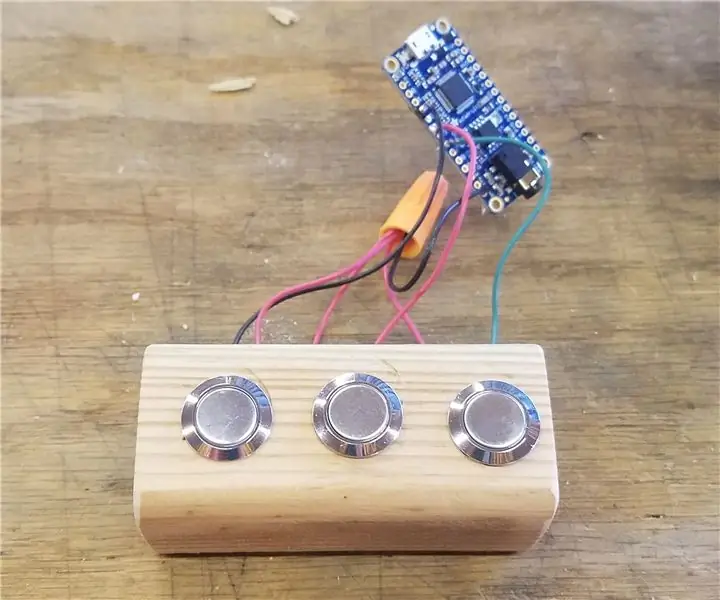

3 veiksmas: išorinio garsiakalbio prijungimas

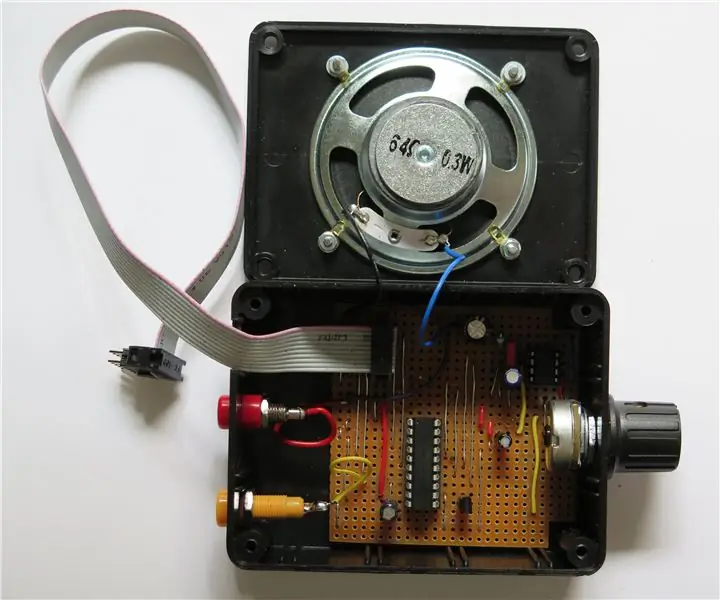

Norėdami prijungti išorinį garsiakalbį prie „Basys3“plokštės, paimkite du laidus ir prijunkite juos, kaip nurodyta aukščiau esančiame paveikslėlyje. Balta linija jungia neigiamą garsiakalbio gnybtą prie plokštės įvado. Raudona linija jungia teigiamą garsiakalbio gnybtą prie plokštės JA10 pmod prievado.

Apribojimų failas sukurtas taip, kad bet koks prievadas nuo JA1 iki JA10 turėtų veikti. Tačiau kai kurie lentos kaiščiai nereaguoja, todėl, jei JA10 neveikia, galite išbandyti kitus prievadus.

4 žingsnis: struktūrinė diagrama

Aukščiau esančiame paveikslėlyje parodyta konkurencinės signalizacijos sistemos struktūrinė schema, apimanti visus komponentus, sudarančius pagrindinį modulį. Jų aprašymai yra tokie:

player_lockout_LED1 Grotuvo užrakinimo šviesos diodų komponentas yra baigtinės būsenos aparatas, kuris naudoja vieno karšto kodavimą. Jame yra keturi įėjimai: player1, player2, reset ir CLK. Jame yra 2 bitų paketo išvesties grotuvas_LED. „Player_lockout_LED1“komponento įėjimai ir išėjimai yra tiesiogiai prijungti prie identiškai pavadintų pagrindinio modulio įėjimų ir išėjimų.

buzzer_tone1 „Buzzer“komponentas yra pagrįstas šiuo kodu, paskelbtu forume

stackoverflow.com/questions/22767256/vhdl- … Tačiau jis buvo pakeistas taip, kad išleistų nenutrūkstamą 440 Hz dažnio garsą (pastaba). Įjungimo įvestis prijungta prie signalo „buzzer_enable“, kuris yra „down_counter_FSM1“komponento išėjimas.

clk_div1 Laikrodžio daliklio komponentas yra modifikuota profesoriaus Bryano Mealy laikrodžio daliklio versija, pateikta „PolyLearn“. Jis sulėtina laikrodį, todėl išvesties laikotarpis yra 1 sekundė.

down_counter_FSM1 Žemutinis skaitiklis yra FSM, sukurtas skaičiuoti iki nulio. Du galimi pradžios laikai yra 20 arba 5, kuriuos pasirenka vartotojo įvestis. Kai laikmatis pasiekia nulį, jis išleidžia „1“, rodydamas, kad laikas baigėsi. Ši išvestis veikia kaip garsinio signalo komponento įgalinimas. Skaitiklis taip pat išleidžia 8 bitų paketo signalą, kuris siunčia 8 bitų BCD, kuris siunčiamas į segmento dekoderį. Kitas išėjimas yra counter_on, kuris taip pat yra prijungtas prie galiojančio segmento dekoderio įvesties.

sseg_dec1 Septynių segmentų dekoderio komponentas pateikiamas „PolyLearn“ir jį parašė profesorius Bryanas Mealy. Jis naudoja BCD įvestį, pateiktą „down_counter_FSM1“, ir septynių segmentų ekrane pateikia dešimtainį atitikmenį. Kai skaitiklis įjungtas, galiojanti įvestis yra didelė. Tai leidžia dekoderiui rodyti dešimtainį skaičių septynių segmentų ekrane. Kai skaitiklis išjungtas, galiojanti įvestis yra maža. Septynių segmentų ekrane bus rodomi tik keturi brūkšniai.

5 žingsnis: baigtinės būsenos mašinos (FSM) diagrama

Ribotos būsenos mašinos jautrumo sąraše yra grotuvas1, grotuvas2, atstatymas ir laikrodis. FSM išvestis yra 2 bitų paketas „player_LED“, prijungtas prie dviejų šviesos diodų „Basys3“plokštėje. Baigtinės būsenos mašina rodo šias tris būsenas:

ST0 yra pradžios būsena. Esant šiai būsenai, du šviesos diodai yra išjungti. FSM liks šioje būsenoje, jei tiek 1 žaidėjo, tiek 2 žaidėjo bus mažai. Asinchroninis atstatymas taip pat nustato būseną į ST0. Kai „player1“jungiklis nustatytas aukštai, kita būsena bus ST1. Jei „player2“jungiklis nustatytas aukštai, kita būsena bus ST2.

ST1 yra būsena, kurioje žaidėjas1 šviečia. FSM liks šioje būsenoje bet kokiam įėjimui. Tai reiškia, kad net tada, kai „player2“jungiklis yra nustatytas aukštai iš karto po to, kai „player1“jungiklis yra aukštai, jis liks ST1. Tik asinchroninis atstatymas gali nustatyti kitą būseną į ST0.

ST2 yra būsena, kurioje šviečia „player2“šviesos diodas. Panašiai kaip „ST!“, FSM liks šioje būsenoje bet kokiam įėjimui, net kai „player1“jungiklis yra nustatytas į aukštą iš karto po to, kai „player2“jungiklis yra aukštas. Vėlgi, tik asinchroninis atstatymas gali nustatyti kitą būseną į ST0.

Rekomenduojamas:

Automobilio garso signalas - pasirinktiniai garso efektai: 4 žingsniai (su nuotraukomis)

Automobilio garso signalas - pasirinktiniai garso efektai: Įrengiau savo automobilyje pasirinktinius garso signalų efektus, remdamasis „Mark Rober“„YouTube“vaizdo įrašais, ir man patinka daryti daiktus. Mano nuomone, pagrindiniam automobilio garso signalui reikia daugiau galimybių veiksmingam vairuotojų bendravimui. Ten, kur esu iš standartinio automobilio rago, yra

Wiggly Wobbly - pamatykite garso bangas !! Realaus laiko garso vizualizatorius !!: 4 žingsniai

Wiggly Wobbly - pamatykite garso bangas !! Garso vizualizatorius realiuoju laiku !!: Ar kada susimąstėte, kaip atrodo „Beetle“dainos? Arba jūs tiesiog norite pamatyti, kaip atrodo garsas? Tada nesijaudinkite, aš esu čia, kad padėtų jums tai padaryti! !!! Pakelkite garsiakalbį aukštai ir siekite išblukusio

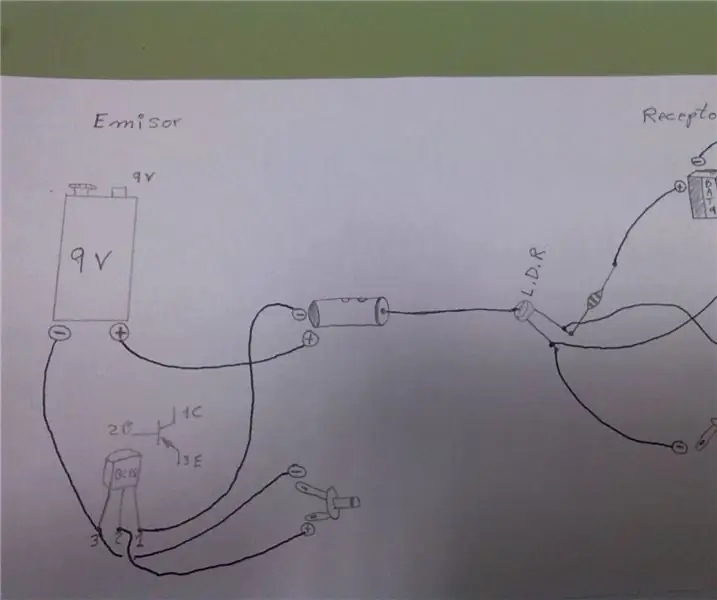

Garso ir garso perdavimo lazeriu konstrukcija: 3 žingsniai

Garso ir garso perdavimo lazeriu konstrukcija: lazerio konstrukcija ir garso perdavimas

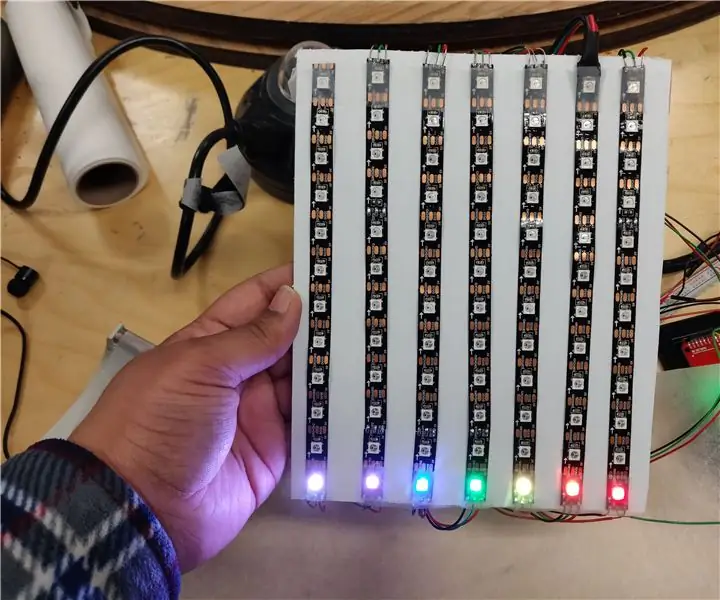

7 juostų garso garso vizualizatorius: 4 žingsniai (su nuotraukomis)

7 juostų garso garso vizualizatorius: tai projektas, kuris priima nuolatinį analoginį signalą, paprastai muziką, ir naudoja jį 7 juostų LED vizualizatoriui įjungti. Jis naudoja MSGEQ7 mikroschemą muzikos signalui analizuoti, kad gautų dažnio dydžius ir susietų su LED juostomis. „Led“juostelės

Garso garso failų (Wav) leidimas naudojant „Arduino“ir DAC: 9 žingsniai

Garso garso failų (Wav) leidimas naudojant „Arduino“ir DAC: atkurkite „wav“garso įrašą iš savo „Audino“SD kortelės. Ši instrukcija parodys, kaip „SdCard“wav failą galima paleisti per paprastą grandinę garsiakalbiui. „Wav“failas turi būti 8 bitų monofoninis. Aš neturėjau problemų atkurdamas 44 KHz failus. Nors ne