Turinys:

- 1 žingsnis: Blokinė diagrama

- 2 žingsnis: veikimo principas

- 3 žingsnis: logikos diegimas

- 4 žingsnis: Aklavietės sprendimas

- 5 veiksmas: įrenginio konfigūravimas - „Matrix0“grandinė

- 6 veiksmas: įrenginio konfigūravimas - SPI laikrodžio logika

- 7 veiksmas: įrenginio konfigūravimas - „Matrix0 Components Properties“

- 8 veiksmas: įrenginio konfigūravimas - „Matrix1“grandinė

- 9 veiksmas: įrenginio konfigūravimas - 3 bitų dvejetainis skaitiklis

- 10 veiksmas: įrenginio konfigūracija - 3 bitų palyginimo logika

- 11 veiksmas: įrenginio konfigūravimas - skaitmeninis palyginimo logika ir laikinas registras

- 12 žingsnis: Įrenginio konfigūravimas - „Matrix1“komponentų ypatybės

- 13 žingsnis: Rezultatai

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:45.

- Paskutinį kartą keistas 2025-01-23 14:58.

Valdymo sistemos ir susiję įrenginiai naudoja kelis maitinimo šaltinius, pvz., Šališkąsias linijas ar baterijas, ir turi sekti aukščiausią (arba žemiausią) liniją tarp tam tikro rinkinio.

Pvz., Apkrovos perjungimas „kelių baterijų“maitinimo sistemoje reikalauja, kad sistema stebėtų minimalią arba maksimalią įtampą tarp akumuliatorių bloko (maks. Arba min. Kaip konkretaus perjungimo algoritmo funkcija) ir dinamiškai nukreiptų krovinį į tinkamiausias šaltinis realiu laiku. Arba, norint tinkamai įkrauti, sistemai gali tekti laikinai atjungti žemiausios įtampos akumuliatorių.

Kitas pavyzdys - šiuolaikinė saulės energijos sistema, kurioje kiekvienas saulės kolektorius turi pasukimo mechanizmą ir saulės sekimo grandinę (pastaroji pateikia informaciją apie Saulės padėtį, kad būtų galima orientuoti skydelį). Turint maksimalios įtampos informaciją, kiekviena saulės kolektoriaus padėtis gali būti tiksliai sureguliuota, remiantis stygos skydeliu, kuris iš tikrųjų tiekia aukščiausią išėjimo įtampą, taip pasiekiant aukščiausią galios optimizavimo lygį.

Yra keletas skirtingų komercinių IC ženklų (daugiausia mikrovaldiklių), kurie iš esmės gali įdiegti maksimalios įtampos sekiklį. Tačiau jie reikalauja programavimo ir yra mažiau ekonomiški nei mišraus signalo sprendimas. „Dialog GreenPAKTM“dizaino papildymas gali teigiamai paveikti dizaino prieinamumą, dydį ir moduliarumą. Ši konstrukcija išnaudoja pranašumą integruojant tiek analogines, tiek skaitmenines grandines į vieną mikroschemą.

Šioje instrukcijoje yra įdiegta analoginė priekinė dalis ir skaitmeninė logika, reikalinga maksimaliai (arba galiausiai min) įtampos ieškikliui įgyvendinti tarp aštuonių skirtingų šaltinių.

8 kanalų analoginiam maksimalios/minutės įtampos monitoriui įgyvendinti naudojamas SLG46620G.

Žemiau aprašėme veiksmus, kurių reikia norint suprasti, kaip sprendimas buvo užprogramuotas, kad būtų sukurtas 8 kanalų analoginis maksimalios/min. Įtampos monitorius. Tačiau, jei norite gauti programavimo rezultatą, atsisiųskite „GreenPAK“programinę įrangą, kad peržiūrėtumėte jau užpildytą „GreenPAK“dizaino failą. Prijunkite „GreenPAK Development Kit“prie kompiuterio ir paspauskite programą, kad sukurtumėte 8 kanalų analoginį maksimalios/min. Įtampos monitorių.

1 žingsnis: Blokinė diagrama

1 paveiksle pavaizduota įdiegtos sistemos bendra schema.

Iki 8 kintamos įtampos šaltinių eilutė yra multipleksuota ir sujungta su „GreenPAK“ADC moduliu, prijungtu prie pritaikyto vidinio dizaino, galinčio pasirinkti aukščiausios įtampos šaltinį kitų atžvilgiu. Vidinė logika pateikia šią informaciją rodymui ar tolesniam apdorojimui.

Dizainas pagrįstas „GreenPAK SLG46620G“produktu, nes jame yra visi programai reikalingi analoginiai ir skaitmeniniai blokai. Šiuo atveju masyvas nuskaitomas naudojant analoginį ADG508 multiplekserį, tiesiogiai valdomą „GreenPAK IC“.

Išvesties informacija yra 3 bitų skaitmeninis skaičius, atitinkantis įtampos šaltinio numerį esant maksimaliai įtampai. Tiesioginis būdas gauti šią informaciją yra rodyti numerį per 7 segmentų ekraną. Tai galima lengvai padaryti prijungus SLG46620G skaitmeninę išvestį prie 7 segmentų ekrano tvarkyklės, pvz., „GreenPAK“sprendimo, aprašyto „Nuorodoje“, arba prie bendro 74LS47 IC.

Pateiktoje grandinėje ieškoma maksimalios įtampos. Norėdami konstrukciją paversti minimalios įtampos ieškikliu, tarp analoginio multiplekserio ir „GreenPAK“analoginės įvesties reikia pridėti paprastą išankstinio kondicionavimo grandinę, atimant multipleksoriaus išėjimą iš 1 V etaloninės įtampos.

2 žingsnis: veikimo principas

Projektuojant siekiama pasirinkti maksimalios įtampos šaltinį, todėl nuskaitymas atliekamas visam masyvui, išsaugojant paskutinę maksimalią vertę ir lyginant ją su kita įvesties verte (kuri priklauso kitam nuskaitymo įtampos šaltiniui).

Toliau mes vadinsime visą multipleksavimo seką išilgai visų įėjimų kaip „nuskaitymą“arba „ciklą“.

Dviejų verčių palyginimas atliekamas ne naudojant ACMP komponentus (tačiau juos galima rasti SLG46620G), o naudojant DCMP modulį, kai vertės atitinkamai suskaitmeninamos. Tai pažangi ir patobulinta technika, pirmą kartą aptarta „Nuorodoje“.

2 paveiksle parodyta, kaip SLG46620G yra suprojektuotas pagal šį dizainą.

Analoginis įvesties signalas eina į ADC įvestį per PGA komponentą, nustatant stiprumą 1. Įvairūs stiprinimo nustatymai taip pat galimi, kad būtų galima rasti geriausią suderinamumą su priekine kondicionavimo elektronika, skirta įvesties įtampai susieti su 0-1 V „GreenPAK ADC“modulio asortimentą.

ADC veikia vieno galo režimu ir konvertuoja analoginį signalą į 8 bitų skaitmeninį kodą, kuris vėliau perkeliamas į DCMP modulį. Skaitmeninis kodas taip pat įvedamas į SPI bloką, sukonfigūruotą kaip ADC/FSM buferis, kuriame galima išsaugoti skaitmeninį kodą ir jis nepasikeis, kol kitas impulsas nepateks į SPI CLK įvestį. Atkreipkite dėmesį, kad specialus loginis blokas valdo SPI CLK įvestį. Šią dalį išnagrinėsime vėliau, nes tai yra „pagrindinė“logika, atsakinga už tinkamą veikimą. Naujas skaitmeninis kodas saugomas SPI modulyje tik tuo atveju, jei jis priklauso faktinei maksimaliai įėjimo įtampai.

DCMP komponentas naudojamas dabartiniams ADC duomenims palyginti su paskutiniu laimėtoju (tai yra paskutinis rastas maks.), Kuris saugomas SPI bloke. Jis generuos impulsą OUT+ išvestyje, kai nauji ADC duomenys bus didesni nei ankstesni. Mes naudojame OUT+ signalą, kad atnaujintume SPI bloką nauju laimėtoju.

Pasaulinis laikrodžio signalas skatina ADC konversijas ir bendrą laiką. Kai konversija atliekama, ADC INT išėjimo signalo impulsai, laiku suderinami su ADC lygiagrečių duomenų išvestimi. Mes taip pat naudojame INT išvestį, kad padidintume 3 bitų dvejetainį skaitiklį, kurį DFF įdiegė „Matrix1“, o tai naudinga dėl trijų priežasčių:

1. Skaitiklio išvesties linijos adresuoja išorinį analoginį multiplekserį, taip tiekiant kitą įėjimo įtampą ADC;

2. Skaičius yra įšaldomas į 3 bitų registrą (įdiegtą „Matrix1“), kad nuskaitymo metu būtų saugomas laikinasis nugalėtojas;

3. Skaičius yra iššifruojamas, kad būtų atnaujintas antrasis 3 bitų registras (įdiegtas „Matrix0“), kai nuskaitymas bus baigtas.

3 žingsnis: logikos diegimas

ADC modulis vieną po kito neribotą laiką teikia konvertuotus visų įėjimo įtampų duomenis. Kai multiplekseris yra adresuotas 0b111 (dešimtainis skaičius), skaitiklis nusileidžia iki 0b000 (dešimtainis), taip pradedamas naujas įvesties įtampos nuskaitymas.

Nuskaitymo metu ADC INT išvesties signalas generuojamas, kai galioja lygiagretus duomenų išvestis. Kai šis signalas impulsuoja, analoginis multiplekseris turi persijungti į kitą įvestį, tiekdamas PGA atitinkamą įtampą. Todėl ADC INT išėjimas yra tiesioginis laikrodžio signalas, pateiktas 2 paveikslo 3 bitų dvejetainiame skaitiklyje, kurio 3 bitų lygiagretus išvesties žodis tiesiogiai kreipiasi į išorinį analoginį multiplekserį („V select“1 paveiksle).

Dabar pažiūrėkime į pavyzdį, kai įėjimo įtampa turėtų turėti šiuos ryšius:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

3 paveiksle pavaizduoti pagrindiniai signalai, susiję su maksimalaus sprendimo mechanizmu.

Kadangi duomenys galiausiai įrašomi į SPI buferio registrą sinchroniškai su INT impulsais, yra palyginimo langas, kuriame SPI buferio turinys lyginamas su kitu ADC konversijos rezultatu. Dėl šio konkretaus laiko DCMP išvestyje generuojami OUT+ impulsai. Mes galime pasinaudoti šiais impulsais ir įkelti naujas vertes į SPI buferio registrą.

Kaip matyti iš ankstesnio paveikslo SPI buferio duomenų eilutės, SPI registre visada yra didžiausia reikšmė tarp 8 įėjimų ir jis atnaujinamas tik tada, kai DCMP modulis aptinka didesnę vertę (nuoroda į DCMP) OUT+ grafiko išvesties linija, dėl trūkstamų impulsų V2 lieka užrakintas registre, palyginti su V5).

4 žingsnis: Aklavietės sprendimas

Jei įdiegta logika būtų tokia, kaip aprašyta aukščiau, akivaizdu, kad patektume į aklavietę: sistema sugeba aptikti tik aukštesnę įtampą nei ta, kuri atitinka SPI buferio registrą.

Tai taip pat galioja tuo atveju, jei ši įtampa sumažėtų, o kitas įėjimas, iki šiol mažesnis už jį, tampa didžiausias: jis niekada nebūtų aptiktas. Ši situacija geriau paaiškinta 4 paveiksle, kur yra tik 3 įėjimo įtampos. aiškumo.

2 iteracijos metu V3 sumažėja, o V1 yra faktinė maksimali įtampa. Tačiau DCMP modulis nesuteikia impulsų, nes duomenys, saugomi SPI buferio registre (atitinka 0,6 V), yra didesni nei V1 (0,4 V).

Tada sistema elgiasi kaip „absoliutus“maks. Ieškiklis ir netinkamai atnaujina išvestį.

Puikus būdas išspręsti šią problemą yra priversti iš naujo įkelti duomenis į SPI buferio registrą, kai sistema užbaigia visą visų kanalų apklausos ciklą.

Tiesą sakant, jei įtampa toje įvestyje vis dar yra didžiausia, niekas nesikeičia ir valdymas vyksta saugiai (remiantis 4 paveikslu aukščiau, tai yra 0 ir 1 ciklo pakartojimų atvejis). Kita vertus, jei įtampa toje įvestyje atsitiktinai sumažėja iki vertės, mažesnės už kitą įvestį, tada iš naujo įkeliant vertę, DCMP moduliui suteikiama galimybė gauti OUT+ impulsą, lyginant jį su nauja maksimalia verte (tai yra 2 ir 3 kilpų pakartojimų atvejis).

Norint įveikti problemą, reikalinga loginė grandinė. Kai ciklas pasiekia tikrąją maksimalią įvestį, jis turi generuoti laikrodžio signalą SPI komponentui, taip priversdamas iš naujo įkelti atnaujintą duomenų žodį į SPI buferio registrą. Tai bus aptarta 7.2 ir 7.6 skyriuose.

5 veiksmas: įrenginio konfigūravimas - „Matrix0“grandinė

SLG46620G turi du matricinius blokus, kaip pavaizduota 2 paveiksle. Toliau pateikti paveikslai rodo atitinkamas įrenginio konfigūracijas.

Viršutinė grandinės dalis yra „ciklo registras“, sukurtas naudojant 3 DFF (DFF0, DFF1 ir DFF2). Po kiekvienos įvesties multiplekserio kilpos atnaujinama 7 segmentų ekrano tvarkyklei nusiųsti „laimėtojo“dvejetainis numeris, tai yra įvestis, turinti didžiausią įtampą paskutinio nuskaitymo metu. Tiek laikrodis prie DFF, tiek duomenys gaunami iš „Matrix1“įdiegtos logikos atitinkamai per prievadą P12, P13, P14 ir P15.

Apatinė dalis yra analoginė priekinė dalis su įvestimi 8 kaiščiu ir PGA su stiprinimu x1. ADC INT išėjimas eina tiek į SPI laikrodžio logiką, tiek į „Matrix1“per prievadą P0, kur jis bus naudojamas kaip laikrodžio signalas įgyvendintam skaitikliui.

ADC ir SPI lygiagrečios duomenų išvestys atitinkamai pažymėtos NET11 ir NET15, kad būtų prijungtos prie DCMP komponento „Matrix1“.

6 veiksmas: įrenginio konfigūravimas - SPI laikrodžio logika

Kaip minėta anksčiau skyriuje „Loginis įgyvendinimas“, SPI buferio registras atnaujinamas kiekvieną kartą, kai palyginus faktinę saugomą vertę ir naujus ADC konversijos duomenis, gaunamas impulsas DCMP OUT+ išvestyje.

Signalo vientisumas užtikrinamas, jei šis signalas yra AND-ed su ADC INT išvestimi. Taip išvengiama smaigalių ir klaidingų paleidimų.

Mes taip pat pabrėžėme, kad norint praleisti aklavietės situacijas, SPI buferis turi būti atnaujintas, kai ciklas pasiekia faktinius laimėtojo duomenis.

Tada žaidime yra trys signalai, kaip tinkamai nustatyti SPI:

1. ADC INT išėjimas (LUT0-IN1)

2. DCMP OUT+ išėjimas (LUT0-IN0 per P10 prievadą)

3. Skaičius lygus skląsčio signalui (LUT0-IN2 per prievadą P11)

Pirmieji du yra AND-red, o abu-OR-ed su pastaruoju LUT0, kurio įgyvendinimas sukonfigūruotas kaip 6 paveiksle.

7 veiksmas: įrenginio konfigūravimas - „Matrix0 Components Properties“

7-10 paveiksluose parodyti likę komponentų ypatybių langai, priklausantys „Matrix0“.

8 veiksmas: įrenginio konfigūravimas - „Matrix1“grandinė

9 veiksmas: įrenginio konfigūravimas - 3 bitų dvejetainis skaitiklis

Viršutinėje grandinės dalyje yra loginių elementų, daugiausia 3 bitų dvejetainis skaitiklis, kurį laiko ADC INT išėjimas, kaip jau aptarta. Šis skaitiklis yra įgyvendintas naudojant gana „standartinę“schemą, parodyta 12 paveiksle.

Šis skaitiklis suprojektuotas naudojant šlepetes DFF9, DFF10, DFF11 ir INV1, LUT4, LUT8. DFF9 išvestis yra LSB, o DFF11 yra MSB, kaip parodyta 13 paveiksle.

LUT4 sukonfigūruotas kaip XOR, o LUT8 atlieka 12 paveikslo AND-XOR logiką.

Skaitiklio išėjimai nukreipiami į tris skaitmeninius išvesties kaiščius, kad būtų galima adresuoti išorinį analoginį multiplekserį.

LUT10 dekoduoja skaitiklio kodą, kai nuskaitymas yra baigtas, ir perduoda impulsą į „Matrix0“per DLY8 ir prievadą P12. Tai paprasčiausiai pasiekiama AND įvedus skaitiklio išėjimus, taip iššifruojant skaičių 7 dec (0b111 dvejetainis, ciklo pabaiga).

10 veiksmas: įrenginio konfigūracija - 3 bitų palyginimo logika

15 paveiksle parodyta grandinė, naudojama aptikti, kada kilpa kartojasi dabartiniu „nugalėtojo“adresu. Šiuo atveju, kaip jau aptarta, skaitmeninis impulsas turėtų priversti iš naujo įkelti dabartinį ADC rezultatą, kad išspręstų galimą aklavietės situaciją.

„Laimėtojo“adresas yra saugomas laikinajame „Matrix1“registre (žr. Toliau), o dabartinį adresą išves dvejetainis skaitiklis.

XNOR vartai suteikia tikrą (loginę 1 arba „aukštą“) išvestį, kai abu įėjimai yra lygūs. IR šio signalo įvedimas visiems bitams (LUT9) suteikia mums impulsą, kai abu dvejetainiai kodai yra vienodi. Išsamią informaciją apie XOR vartus, kaip pariteto tikrintuvą, rasite nuorodoje.

„Counter-equals-Latch“signalas perduodamas „Matrix0“per prievadą P11.

11 veiksmas: įrenginio konfigūravimas - skaitmeninis palyginimo logika ir laikinas registras

Apatinėje 11 paveikslo dalyje (paryškinta 16 paveiksle) parodytas DCMP blokas, sprendimų priėmimo dalis.

DFF6, 7 ir 8 sudaro 3 bitų registrą, kuriame saugomas laikinas įvesties numeris „nugalėtojas“, kol ciklas veikia. „Flip-Flops“įvestis yra 3 bitų dvejetainis skaitiklio išėjimas, kaip matoma 11 paveikslo pasaulinėje „Matrix1“grandinėje, čia aiškumo dėlei praleista.

Šio registro išvestys negali tiesiogiai valdyti 7 segmentų ekrano, nes čia saugoma vertė keičiasi nuskaitymo metu ir turėtų būti laikoma „galiojančia“tik paties nuskaitymo pabaigoje.

Dėl šios priežasties laikini registro išėjimai jungiasi prie „Matrix0“ciklo registro per tarpmatricinius prievadus P13, P14 ir P15.

16 paveiksle svarbu pastebėti, kad laikinasis registras yra fiksuojamas naudojant DCMP OUT+ išvestį, kai ADC-SPI registrų palyginimo rezultatas yra naujas.

Tas pats OUT+ signalas perduodamas „Matrix0“, „SPI CLK Logic“per prievadą P10.

12 žingsnis: Įrenginio konfigūravimas - „Matrix1“komponentų ypatybės

17-19 paveiksluose parodyti „Matrix1“priklausantys komponentų ypatybių langai.

13 žingsnis: Rezultatai

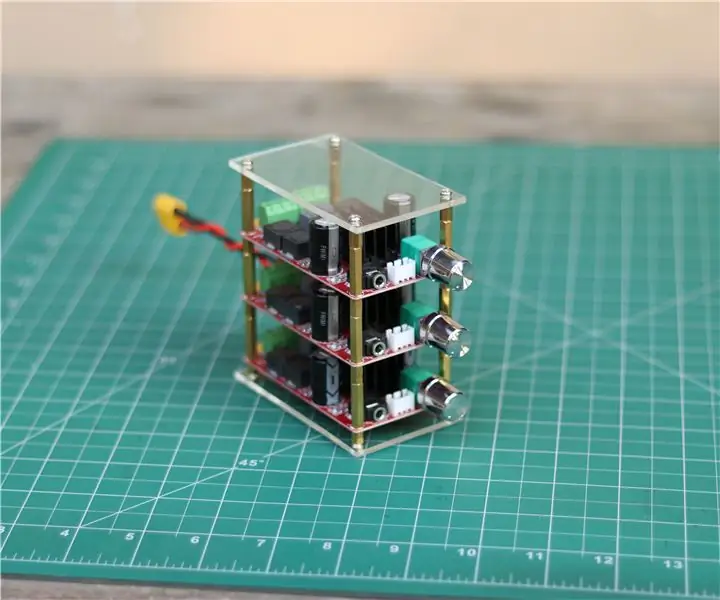

Norėdami išbandyti įgyvendinimą, buvo sukurtas vertinimo plokštės prototipas, kuriame 8 analoginės įvesties įtampos gaunamos naudojant rezistorių daliklius su „TrimPots“(kaip parodyta 20 paveiksle).

Naudojamas multiplekseris ADG508, dalis, kuri gali veikti su vienu maitinimu (12 V).

7 segmentų ekrano tvarkyklė yra 74LS47. Jis dekoduoja lygiagretų įvesties žodį ir tiesiogiai valdo 7 segmentų bendrojo anodo ekraną.

Vertinimo lenta turi 2x10 stačiakampę jungtį, kurią galima tiesiogiai prijungti prie „GreenPAK Advanced Development Platform“prie jos išplėtimo jungties, kaip parodyta 21 paveiksle.

Kartu su „GreenPAK Advanced Development Platform“labai paprasta išmatuoti signalus, kad būtų galima greitai patikrinti. Pavyzdžiui, 22 paveiksle pavaizduotas signalų rinkinys (atitinkamai CLOCK, ADC INT išvestis ir DCMP OUT+ išvestis), užfiksuotas HP 54620A loginio analizatoriaus. Bangos formos suaktyvinamos kylančiu OUT+ signalo kraštu (apimtyje, pažymėtoje kaip „A> B“), todėl tai yra bangos formos fiksavimas, kai tarp analoginių įėjimų aptinkama nauja maksimali įtampa. Tiesą sakant, jis buvo gautas sukant vieną iš vertinimo lentos „TrimPots“, kad padidėtų atitinkama įtampa, parodyta 22 paveiksle.

23 paveiksle parodyta vertinimo tarybos schema.

Išvada

Šioje instrukcijoje mes įdiegėme aštuonių kanalų maksimalios (arba min) įtampos ieškiklį, kuris bus naudojamas kaip bendras daugelio kanalų valdymo sistemų priedas. Pateiktas metodas naudoja pažangias „GreenPAK“komponentų funkcijas ir parodo, kaip galima integruoti į vieną mikroschemą analogines ir skaitmenines funkcijas. Keli komerciniai IC gali būti pakeisti „Dialog GreenPAK“, kad būtų sumažintas programos dydis ir kaina.

Rekomenduojamas:

Aukštos įtampos baterijų įtampos monitorius: 3 žingsniai (su paveikslėliais)

Aukštos įtampos akumuliatorių įtampos monitorius: Šiame vadove aš jums paaiškinsiu, kaip aš sukūriau savo akumuliatoriaus įtampos monitorių savo elektriniam longboardui. Sumontuokite jį kaip norite ir prijunkite tik du laidus prie akumuliatoriaus (Gnd ir Vcc). Šiame vadove daroma prielaida, kad jūsų akumuliatoriaus įtampa viršija 30 voltų

Sukurkite mini „pasidaryk pats“hidroponines sistemas ir pasidaryk pats „Hydroponic Herb Garden“su „WiFi“įspėjimais: 18 žingsnių

Sukurkite mini „pasidaryk pats“hidroponines sistemas ir pasidaryk pats „Hydroponic Herb Garden“su „Wi -Fi“įspėjimais: šioje pamokoje parodysime, kaip sukurti #DIY #hidroponikos sistemą. Ši „pasidaryk pats“hidroponinė sistema laistys pagal pasirinktą hidroponinį laistymo ciklą, 2 minutes įjungus ir 4 minutes išjungus. Jis taip pat stebės rezervuaro vandens lygį. Ši sistema

„Pasidaryk pats“300 vatų 5.1 kanalų stiprintuvas: 12 žingsnių (su nuotraukomis)

Pasidaryk pats 300 vatų 5.1 kanalų stiprintuvas: Ei! visi Mano vardas Steve. Šiandien aš jums parodysiu, kaip sukurti 5.1 kanalų stiprintuvą Spustelėkite čia, kad pamatytumėte vaizdo įrašą Pradėkime

Atnaujinkite „pasidaryk pats“laistymo puodą su „WiFi“į „pasidaryk pats“judesio aptikimo signalizacijos signalą 17 žingsnių

Atnaujinkite „pasidaryk pats“laistymo puodą su „WiFi“į „pasidaryk pats“judesio aptikimo signalizatorių sėjamoji: Šiame straipsnyje mes parodysime, kaip patobulintą savaiminio laistymo puodą su „WiFi“atnaujinti į „pasidaryk pats“laistymo puodą su „WiFi“ir judesio aptikimo signalizacija. Jei neskaitėte straipsnio apie tai, kaip sukurti „pasidaryk pats“laistymo puodą su „WiFi“, galite baigti

8 kanalų analoginis stiprintuvas asmeniniam kompiuteriui ar namams Teatras: 12 žingsnių (su paveikslėliais)

8 kanalų analoginis stiprintuvas asmeniniam kompiuteriui ar namų teatrui: tai pirmas pamokomas dalykas. Aš išmokysiu jus padaryti 8 kanalų stiprintuvą kompiuteriui ar garso sistemai su atskirais analoginiais išėjimais, aš jį naudoju savo staliniame kompiuteryje, žiūrėdamas filmus, klausydamasis HD muzikos ir žaisdamas žaidimus, papildomai