Turinys:

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:48.

- Paskutinį kartą keistas 2025-01-23 14:59.

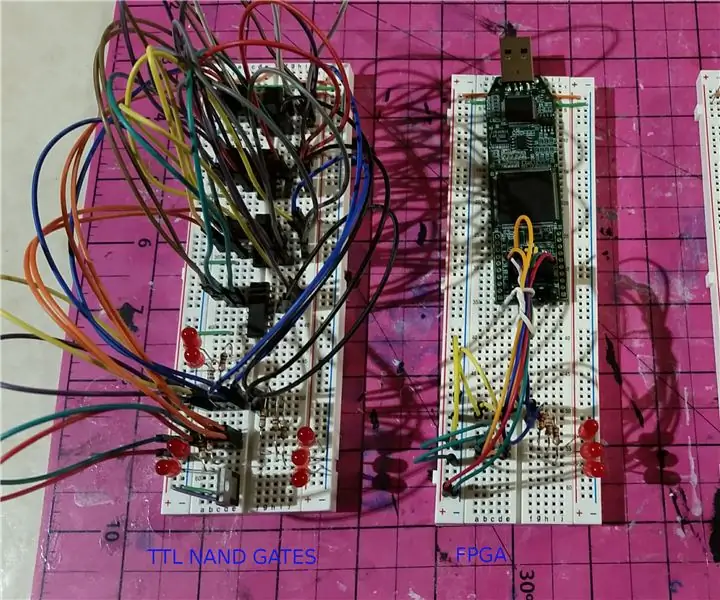

Aparatinės logikos grandinių kūrimas gali būti įdomus. Senas mokyklos būdas tai padaryti buvo su NAND vartais, ant duonos lentos, sujungtos su trumpikliais. Tai vis dar įmanoma, tačiau nereikia daug laiko, kol vartų skaičius išeis iš rankų. Naujausia galimybė yra naudoti FPGA (lauko programuojamų vartų masyvą). Šios mikroschemos gali persijungti ir tapti bet kokia jūsų sukurta skaitmenine logine grandine, tačiau nėra pigios ir lengvai prieinamos. Aš parodysiu, kaip šią FPGA galima pakeisti pigia „Atmega“mikroschema iš „Arduino UNO“, efektyviai įdėjus skaitmeninę grandinę į DIP paketą, kuris yra labai patogus.

1 žingsnis: suprojektuokite grandinę, kurią atstovaus „FPGA“

Aš sukursiu 2 bitų + 2 bitų papildinį. Tam reikia dviejų porų loginių įvesties kaiščių ir išvedama viena tripletas išvesties kaiščių.

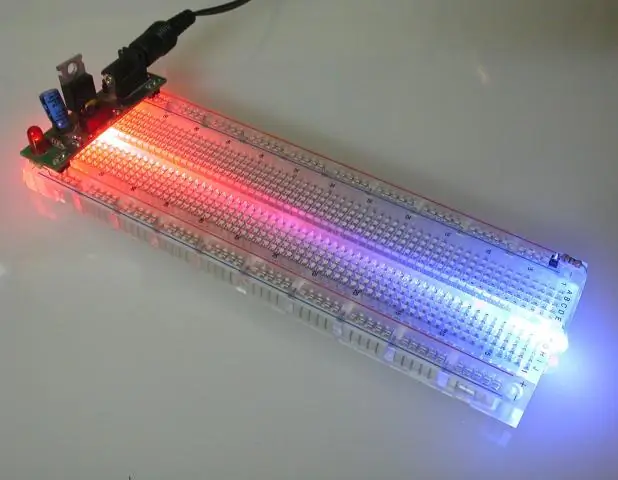

Norėdami tai padaryti naudodami NAND vartus, žiūrėkite schemą paveikslėlyje. Tam reikia 14 NAND vartų. Aš naudojau 4 keturių NAND vartų TTL lustus ir prijungiau juos prie duonos lentos.

Pridėjau keletą šviesos diodų (nepamirškite srovės ribojimo rezistorių), kad parodytumėte, kada įvesties ir išvesties kaiščiai buvo įjungti (aukšti) ir kada jie buvo išjungti (žemi). Norėdami įvesti įvesties kaiščius, aš juos perjungiau į antžeminį bėgį arba teigiamos galios bėgelį.

Ši grandinė veikia, tačiau ji jau užima 4 TTL lustus ir yra žiurkių laidų lizdas. Jei reiktų daugiau gabalėlių, būtų daugiau duonos lentų ir daugiau džemperių. Labai greitai grandinės dydis iškris iš rankų.

Atminkite, kad dirbdami su TTL vartais jie neišleidžia tiksliai 0V ar 5V, kaip galima būtų tikėtis. Jie dažnai išleidžia apie 3 V „aukštai“, tačiau tiksli įtampa yra labai plati. Ta pati grandinė, kurioje naudojami CMOS lygiaverčiai lustai, būtų geriau tiksliai nuo 0V iki tiksliai 5V.

2 veiksmas: įveskite FPGA

FPGA yra fantastiškas lustas, kuris pažodžiui gali tapti bet kokiu loginių vartų deriniu, sujungtu bet kokiu deriniu. Vienas projektuoja „grandinę“aparatinės įrangos kūrimo kalba (HDL). Yra kelios tokios kalbos, viena iš jų vadinama „Verilog“. Paveikslėlyje esantis.v failas yra dviejų bitų papildymo „Verilog“atitikmuo. Žemiau esantis.pch failas taip pat reikalingas norint priskirti įvesties ir išvesties kaiščius, nurodytus verilog faile, prie tikrų mikroschemos aparatūros kaiščių.

Šiuo atveju naudoju „Lattice Semiconductors iCEstick“kūrimo plokštę (https://www.latticesemi.com/icestick). Tikrasis FPGA lustas yra „iCE40HX-1k“su šiek tiek daugiau nei 1000 vartų, kurie gali tapti bet kokiais loginiais vartais. Tai reiškia, kad kiekvienas vartas gali būti NAND vartas, arba OR vartai, NE vartai, NOR, XOR ir tt Be to, kiekvienas vartas gali valdyti daugiau nei du įėjimus. Tai būdinga kiekvienam gamintojui, tačiau iCE40 kiekvienas vartas gali valdyti 4 įėjimus. Taigi kiekvienas vartas yra daug pajėgesnis nei 2 įvesties NAND vartai.

Turėjau priskirti 4 įvesties pušies ir 3 išvesties kaiščius fiziniams kaiščiams 91, 90, 88, 87, 81, 80 ir 79. Tai būdinga „fpga“mikroschemai ir išjungimo plokštei, kurioje ji yra, ir kaip tie kaiščiai yra prijungti prie PMOD prievado. Tai galima rasti šios FPGA plokštės duomenų lapuose.

„Lattice“teikia savo įrankių grandinę, skirtą sintezuoti (FPGA, atitinkanti kompiliaciją CPU) grandines iš „Verilog“, tačiau aš naudojau nemokamą atvirojo kodo įrankių grandinės „icestorm“(https://www.clifford.at/icestorm/). Diegimo instrukcijas rasite toje svetainėje. Įdiegus „icestorm“, „verilog“ir „pcf“failus, komandos įkelti šią grandinę į FPGA yra šios:

yosys -p "synth_ice40 -blif twoBitAdder.v" twoBitAdder.blif

arachne -pnr -d 1k -p iCEstick.pcf twoBitAdder.blif -o twoBitAdder.asc

ledo pakuotė twoBitAdder.asc twoBitAdder.bin

iceprog twoBitAdder.bin

Tai veikia puikiai, tačiau įskaitant šios „iCEstick“siuntimą kainuos apie 30 USD. Tai nėra pigiausias skaitmeninės grandinės kūrimo būdas, tačiau jis yra galingas. Jame yra daugiau nei 1000 vartų ir šiai mažai grandinei jis naudoja tik 3 iš jų. NAND vartų atitikmenyje buvo naudojami 14 vartų. Taip yra dėl to, kad kiekvienas vartas gali tapti bet kokio tipo vartais, o kiekvienas vartas iš tikrųjų yra 4 įėjimo vartai. Kiekvienas vartas gali padaryti daugiau. Jei jums reikia daugiau vartų, „iCEstick“turi didesnį brolį su 8000 vartų, o tai kainuoja apie dvigubai. Kiti gamintojai siūlo kitus pasiūlymus, tačiau kaina gali būti gana didelė.

3 žingsnis: nuo FPGA iki Arduino

FPGA yra puikūs, tačiau gali būti brangūs, sunkiai prieinami ir nėra labai draugiški duonai. Duonos lentai draugiškas ir pigus lustas yra „Atmega 328 P“, kuris tiekiamas tvarkingoje DIP pakuotėje, puikiai tinkančioje maudytis. Tai taip pat galima įsigyti už maždaug 4 USD. Tai yra „Arduino UNO“širdis. Žinoma, galite naudoti visą UNO, tačiau būkite pigūs, mes galime ištraukti „Atmega 328 P“iš UNO ir naudoti ją patys. Vis dėlto aš naudoju UNO plokštę kaip „Atmega“programuotoją.

Šiuo metu jums reikės

1. „Arduino UNO“su nuimamu „Atmega 328P“procesoriumi.

2. Kitas „Atmega 328P“su „Arduino“įkrovos įkrovikliu, kuris buvo iš anksto sudegintas, kad pakeistų tą, kurį ketiname išimti iš JTO. (Neprivaloma, darant prielaidą, kad vis tiek norite turėti naudingą UNO).

Tikslas yra paversti verilog failą į arduino projektą, kurį galima įkelti į 328P. „Arduino“yra pagrįstas C ++. Patogiai yra vertėjas iš „Verilog“į „C ++“, vadinamas „Verilator“(https://www.veripool.org/wiki/verilator). „Verilator“yra skirtas naudoti aparatūros dizaineriams, kuriems reikia imituoti savo dizainą, kol jie įsipareigoja naudoti brangią įrangą. „Verilator cross“surenka verilogą į C ++, tada vartotojas pateikia bandymo diržus, kad pateiktų imituojamus įvesties signalus ir įrašytų išvesties signalus. Mes jį naudosime verilogo dizainui įstrigti „Atmega 328P“naudojant „Arduino“įrankių grandinę.

Pirmiausia įdiekite „Verilator“. Vykdykite instrukcijas

Taip pat įdiekite „Arduino IDE“ir patikrinkite, ar jis gali prisijungti prie „Arduino UNO“per USB.

Mes naudosime tą patį verilog failą, kaip ir FPGA, išskyrus tai, kad reikia pakeisti kaiščių pavadinimus. Prie kiekvieno pradžios pridėjau pabraukimą (_). To reikia, nes „arduino“bibliotekose yra antraštės failas, kuris, pavyzdžiui, B0, B001 ir kt., Verčiamas į dvejetainius skaičius. Kiti įvesties kaiščių pavadinimai būtų buvę tinkami, tačiau B0 ir B1 sukeltų konstrukcijos gedimą.

Kataloge, kuriame yra twoBitAdder.v ir iCEstick.pcf, paleiskite:

veriatorius -Siena --cc twoBitAdder.v

Tai sukurs pakatalogį obj_dir, kuriame bus keli nauji failai. Mums reikalingi tik antraštės ir cpp failai VtwoBitAdder.h, VtwoBitAdder.cpp, VtwoBitAdder_Syms.h ir VtwoBitAdder_Syms.cpp.

„Arduino IDE“sukurkite naują eskizą pavadinimu twoBitAdder.ino. Tai sukurs „Ino“failą naujame kataloge, dar vadinamame „twoBitAdder“, jūsų „Arduino“eskizų knygos kataloge. Nukopijuokite „VtwoBitAdder.h“ir „VtwoBitAdder.cpp“failus į šį „Arduino“aplanko aplanką „twoBitAdder“.

Dabar nukopijuokite antraštės failus iš „Verilator“diegimo.

cp/usr/local/share/verilator/include/verilated*.

pagaliau nukopijuokite į std c ++ biblioteką iš https://github.com/maniacbug/StandardCplusplus. Pagal jų diegimo instrukcijas "Tai įdiegta kaip įprasta" Arduino "biblioteka. Išpakuokite platinimo turinį į eskizų knygos aplanką" bibliotekos ". Pavyzdžiui, mano eskizų knyga yra adresu/home/maniacbug/Source/Arduino, todėl ši biblioteka yra/home/maniacbug/Source/Arduino/libraries/StandardCplusplus.

Įdiegę būtinai iš naujo nustatykite „Arduino IDE“.

Dabar pakeiskite twoBitAdder.ino turinį šiuo veiksmu. Tai tikrinimo diržas, kurio tikisi veriatorius, kuris nustato įvesties/išvesties kaiščius, tada cikle, nuskaito įvesties kaiščius, paduoda juos į „VtwoBitAdder“(išverstą mūsų grandinės versiją), tada nuskaito „VtwoBitAdder“išvestis ir taiko juos į išvesties kaiščius.

Ši programa turėtų būti sudaryta ir vykdoma „Arduino UNO“.

4 žingsnis: nuo „Arduino“iki „DIP Chip“duonos lentoje

Dabar, kai programa veikia „Arduino“, mums nebereikia pačios „Arduino“plokštės. Viskas, ko mums reikia, yra procesorius.

Atsargiai išimkite „Atmega 328P“iš „Arduino UNO“lizdo ir pasirinktinai įdėkite jo pakaitalą.

Įdėkite „Atmega 328P“į duonos lentą. Pabaigą padėkite ant duonos lentos. 1 kaištis yra viršutinis kairysis kaištis. 2 kaištis yra kitas žemyn ir taip toliau prie 14 kaiščio, kuris yra apačioje kairėje. Tada kaištis 15 yra apačioje dešinėje, o kaiščiai nuo 16 iki 28 skaičiuojami atgal į dešinę lusto pusę.

Prijunkite 8 ir 22 kaiščius prie žemės.

Prijunkite 7 kaištį prie VCC (+5V).

Prijunkite 16Mhz kvarco kristalą tarp 9 ir 10 kaiščių. Taip pat mažas kondensatorius (22pF) tarp 9 kaiščio ir žemės ir tarp 10 kaiščio ir žemės. Tai suteikia „Atmega 328P“16Mhz laikrodžio greitį. Kitur yra nurodymų, kaip mokyti 328P naudoti vidinį 8Mhz laikrodį, kuris sutaupytų kelias dalis, tačiau tai sulėtintų procesorių.

„Arduino GPIO“prievadai 5, 6, 7 ir 8, kuriuos naudojome įvesties kaiščiams, iš tikrųjų yra fiziniai „Atmega 328P“kaiščiai 11, 12, 13, 14. Tai būtų keturi apatiniai kaiščiai kairėje.

„Arduino GPIO“prievadai 11, 10 ir 9, kuriuos naudojome išvesties kaiščiams, iš tikrųjų yra „Atmega 328P“fiziniai kaiščiai 17, 16, 15. Tai būtų apatiniai trys kaiščiai dešinėje.

Aš prijungiau šviesos diodus prie šių kaiščių, kaip ir anksčiau.

5 žingsnis: Išvada

TTL lustai veikia, tačiau norint juos sukurti, reikia daug. FPGA veikia tikrai gerai, tačiau nėra pigūs. Jei galite gyventi su mažiau IO kaiščių ir mažesniu greičiu, „Atmega 328P“gali būti jūsų lustas.

Turėkite omenyje kai kuriuos dalykus:

FPGA:

Pro

- Gali valdyti didelės spartos signalus. Kadangi nėra CPU, kuris trukdytų apdoroti iki vienos instrukcijos vienu metu, ribojantis veiksnys yra sklidimo delsimas per tam tikros grandinės vartus. Daugeliu atvejų tai gali būti daug greičiau nei laikrodis, pateiktas kartu su lustu. Mano projektuojant, apskaičiuotas vėlavimas būtų leidęs „twoBitAdder“reaguoti į maždaug 100 milijonų įvesties verčių per sekundę (100 MHz) pokyčių, net jei įmontuotas laikrodis yra tik 12 MHz dažnis.

- Kadangi dizainas tampa sudėtingesnis, esamų grandinių veikimas nesumažėja (daug). Kadangi grandinių pridėjimas prie audinio paprasčiausiai įdeda kažką naujo į nepanaudotą nekilnojamąjį turtą, tai neturi įtakos esamoms grandinėms.

- Priklausomai nuo FPGA, turimų IO kaiščių skaičius gali būti labai didelis ir paprastai jie nėra skirti jokiam konkrečiam tikslui.

Con

- Gali būti brangus ir (arba) sunkiai pasiekiamas.

- Paprastai jis tiekiamas BGA pakuotėje, kuriai reikalinga tam tikra pertraukimo plokštė, kuri dirbtų su mikroschema bet kokiame mėgėjiškame projekte. Jei kuriate jį į dizainą naudodami pasirinktinį daugiasluoksnį SMT PCB, tai nėra problema.

- Dauguma FPGA gamintojų teikia savo uždarojo kodo projektavimo programinę įrangą, kuri kai kuriais atvejais gali kainuoti pinigus arba gali turėti licencijos galiojimo datą.

„Arduino“kaip FPGA:

Pro

- Pigu ir lengva gauti. Tiesiog ieškokite „atmega328p-pu“„Amazon“. Jie turėtų būti apie 4 USD už vienetą. Kai kurie pardavėjai juos parduoda po 3 ar 4.

- Tai DIP paketas, tai reiškia, kad puikiai tinka ant duonos lentos su išoriniais kaiščiais.

- Tai 5 V įrenginys, kuris gali palengvinti sąveiką su kitais 5 V įrenginiais.

Con

- ATMEGA328P turi ribotą skaičių IO kaiščių (23), o keli iš jų yra skirti konkrečioms užduotims atlikti.

- Didėjant grandinės sudėtingumui, „Arduino“ciklo metodu paleisto kodo kiekis didėja, o tai reiškia, kad kiekvieno ciklo trukmė yra ilgesnė.

- Net jei grandinės sudėtingumas yra mažas, kiekvienam ciklui reikia daug CPU nurodymų, kad būtų galima gauti įvesties kaiščio vertes, įrašyti išvesties kaiščio vertes ir grįžti į ciklo viršų. Naudojant 16Mhz kristalą, net esant vienai instrukcijai per laikrodžio ciklą, ciklas neveiks daugiau nei 1 milijoną kartų per sekundę (1 MHz). Tačiau daugeliui mėgėjų elektronikos projektų tai yra daug greičiau nei reikia.

Rekomenduojamas:

Kaip padaryti litavimo mažiau duonos lentą: 7 žingsniai

Kaip padaryti, kad lituoklio mažiau duonos lenta: Aš esu vaikas, kuris mėgsta elektroniką kaip hobį. Sukurkite savo duonos lentą ir komentuokite Sekite mane, kad gautumėte daugiau įdomių dalykų. Ieškoti: oluwadimimu342

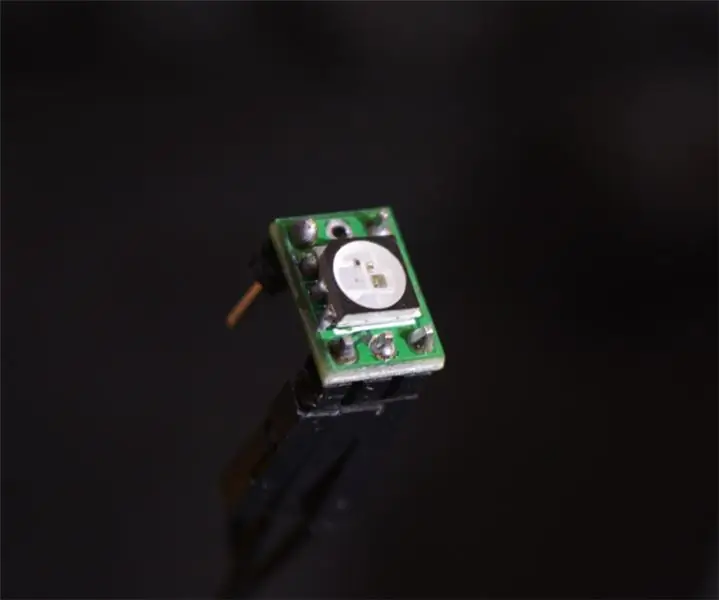

Modulinė neopikselių pertraukimo lenta su atviro kodo duonos lenta: 4 žingsniai (su nuotraukomis)

Modulinė neopikselių pertraukimo lenta su atviro kodo duonos lenta: ši instrukcija yra apie mažytę (8 mm x 10 mm) „Neopixel“šviesos diodams pritaikytą pertraukimo lentą, kurią galima sukrauti ir lituoti viena prie kitos, ji taip pat suteikia daug didesnį konstrukcijos standumą nei plonas LED juostelė daug mažesnėje formoje

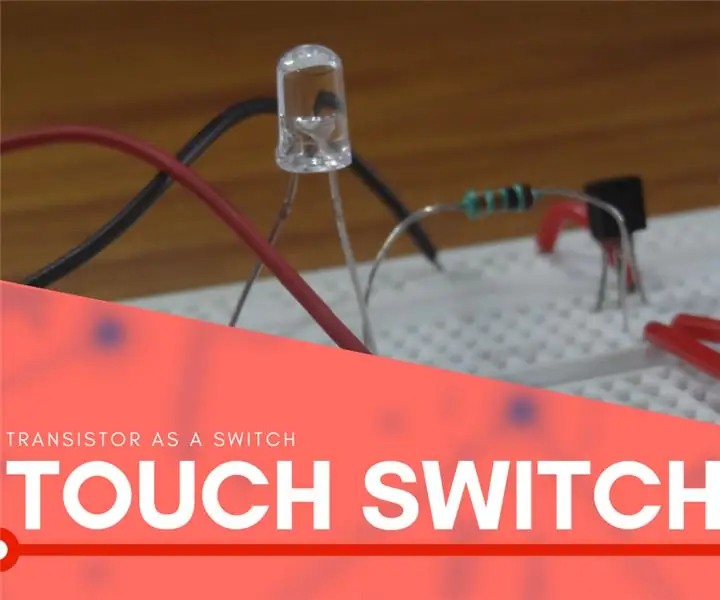

LITTAMASIS JUNGIKLIS - Kaip padaryti jutiklinį jungiklį naudojant tranzistorių ir duonos lentą: 4 žingsniai

LITTAMASIS JUNGIKLIS | Kaip padaryti jutiklinį jungiklį naudojant tranzistorių ir duonos lentą: jutiklinis jungiklis yra labai paprastas projektas, pagrįstas tranzistorių taikymu. Šiame projekte naudojamas tranzistorius BC547, kuris veikia kaip jutiklinis jungiklis. BŪTINAI ŽIŪRĖKITE VIDEO ĮRAŠĄ, KURIUOSIUOSITE IŠSAMIĄ INFORMACIJĄ APIE PROJEKTĄ

Kaip suderinti „Arduino“duonos lentą: 4 žingsniai

Kaip suderinti „Arduino“duonos lentą: Ne paslaptis, kad aplink „oomlout“būstinę esame didžiuliai atviro kodo „Arduino“mikrovaldiklio gerbėjai. Iš anksto paruošta „Duemilanove“lenta yra nuostabi prototipų platforma, tačiau kartais smagu ką nors pasidaryti patiems. Toliau pateikiamas vadovas apie tai, kaip

Duonos lentos išjungimas (kaip pridėti LED maitinimo indikatorių prie skaidrios „Solarbotics“duonos lentos): 7 žingsniai

Išskleiskite savo duonos lentą (kaip pridėti LED maitinimo indikatorių prie skaidrios „Solarbotics“duonos lentos): Šios skaidrios lentos yra panašios į bet kurią kitą elektroninę duonos lentą, tačiau jos yra aiškios! Taigi, ką galima padaryti su skaidria duonos lenta? Manau, akivaizdus atsakymas yra pridėti maitinimo šviesos diodus