Turinys:

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:48.

- Paskutinį kartą keistas 2025-01-23 14:59.

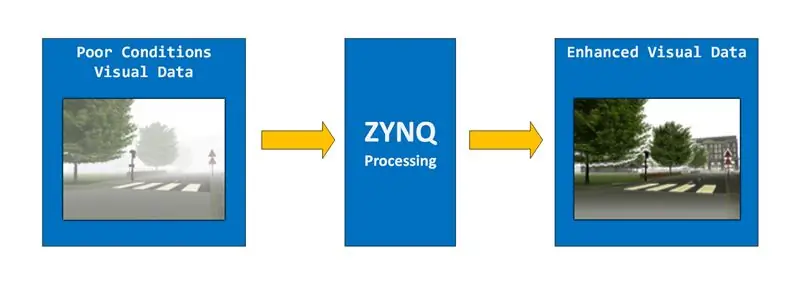

Kaip jūs tikriausiai supratote iš pavadinimo, šio projekto tikslas yra sukurti vaizdo gerinimo sistemą naudojant ZYNQ ApSOC. Tiksliau, mes norime sukurti sistemą, kuri galėtų išvalyti rūkus iš vaizdų ar vaizdo įrašų. Ši sistema paims prastomis sąlygomis vaizdinius duomenis kaip įvestį, apdoros juos naudodami vaizdo gerinimo metodus ir tada išves rezultatą.

Projektas buvo sukurtas ir išbandytas „Digilent Zybo Board“, tačiau turėtų veikti ir kiti ZYNQ įrenginiai.

Šį projektą padalinsime į 3 dalis:

1) INPUT = įvesties vaizdas per eternetą iš kompiuterio/fotoaparato

2) PROCESS = apdoroti vaizdą

3) OUTPUT = išveskite vaizdą per HDMI sąsają

Labai neintuityviai pradėsime nuo projekto išvesties dalies (tai suteiks mums geresnes derinimo galimybes), tęsime įvestį ir baigsime apdorojimo dalimi.

1 žingsnis: medžiagos

Norėdami užbaigti šį projektą, jums reikės:

Aparatūra

- bet kuri ZYNQ plokštė su HDMI ir Ethernet turėtų veikti / aš naudoju „Digilent Zybo“

- USB A - micro B USB kabelis

- HDMI kabelis

- Ethernet kabelis

- Ekranas su HDMI įvestimi

PROGRAMINĖ ĮRANGA

- Xilinx Vivado

- „Xilinx SDK“

2 žingsnis: IŠVESTIS - VGA valdiklis 1 dalis

Vaizdinius duomenis išvesime naudodami plokštėje esantį HDMI prievadą. HDMI prievadas yra prijungtas prie ZYNQ PL (programuojama logika = FPGA) pusės, todėl turėsime jam sukurti VHDL valdiklį. Jei kada nors sukūrėte VGA valdiklį, tai rasite labai panašų. HDMI ir VGA laikai iš tikrųjų yra vienodi, iš tikrųjų galite naudoti esamą VGA valdiklį, kad gautumėte HDMI valdiklį.

Norėdami geriau suprasti, kas iš tikrųjų vyksta, pirmiausia sukursime VGA valdiklį

Norime rodyti 1920x1080 raiška.

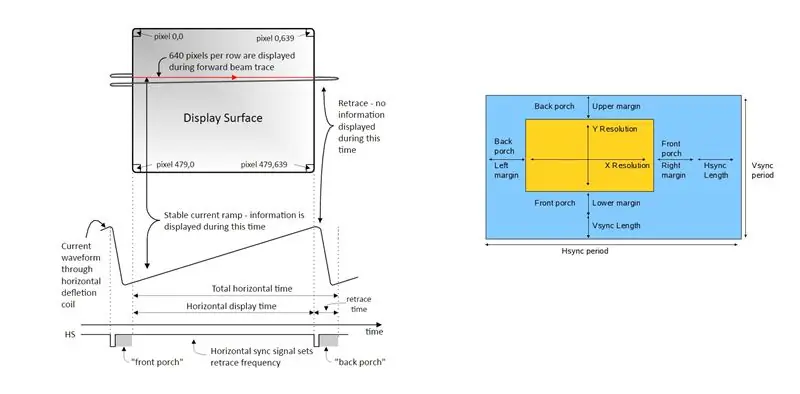

VGA valdiklis yra atsakingas už pikselių duomenų (RGB formatu) perdavimą iš eilės, pikselis po pikselio į ekraną. Be tikrojo 1920x1080 ekrano ploto, taip pat yra keletas „pasienio“zonų, būtent: priekinė veranda, galinė veranda ir trasos. Šių sričių dydis pikseliais yra standartinis ir būdingas kiekvienai skiriamąjai gebai. Šios sritys faktiškai nerodomos ekrane, tačiau jos yra privalomos, o pikselių spalva šioje srityje turi būti juoda. Tinkamas klausimas būtų, kodėl reikalingos šios papildomos sritys. Šis klausimas nepaiso šio pamokomo tikslo, bet jei jums įdomu, raginu jus atlikti tolesnius tyrimus internete.

Tai geras vaizdo įrašas, paaiškinantis VGA sąsają

Mūsų atveju mes norime, kad būtų rodoma 1920*1080 raiška, ir tai yra laikas:

Horizontali ekrano sritis = 1920 pikselių

Horizontali priekinė veranda = 88 pikselių

Horizontali galinė veranda = 148 pikseliai

Horizontalus atsekimas = 44 pikseliai

Vertikalus ekrano plotas = 1080 pikselių

Vertikali priekinė veranda = 4 pikseliai

Vertikali galinė veranda = 36 pikseliai

Vertikalus grįžimas = 5 pikseliai

(Čia rasite kitų rezoliucijų laiką

Taigi mūsų tikroji skiriamoji geba bus 2200 x 1125. Mes norime 60 kadrų per sekundę (kadrų per sekundę), todėl mūsų pikselių laikrodis bus 60*2200*1125 = 148,5 MHz. „Zybo“plokštėje yra 125 Mhz laikrodis. Mes naudosime MMCM IP, kad sukurtume 148,5 MHz pikselių laikrodį, kurio mums reikia.

3 žingsnis: IŠVESTIS - VGA valdiklis 2 dalis

Turėdami teorinį pagrindą iš ankstesnio žingsnio, turėtumėte sugebėti sukurti savo VGA valdiklį. Aš jums pateiksiu „Vivado“projektą, kuris tai daro, bet patariu bent jau pirmiausia pabandyti tai padaryti patiems.

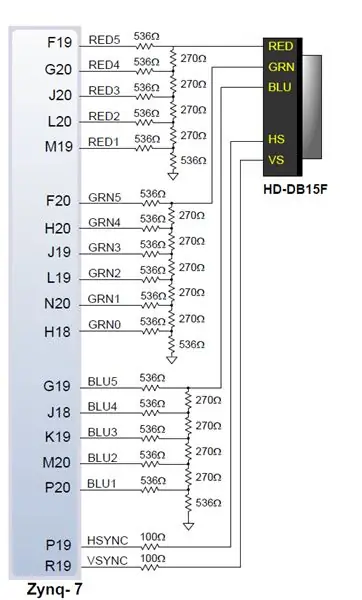

Dauguma VGA prievadų nesuteikia jums 8 bitų kiekvienam spalvų kanalui už pikselį (žr. Paveikslėlį aukščiau), todėl turėsite pritaikyti dizainą prie plokštės pateiktų kaiščių skaičiaus (tačiau tai nėra HDMI problema).

Dizainas visą ekraną nudažys mėlyna spalva, išskyrus viršutinį kairįjį tašką, kuris bus raudonas. Reikėtų pažymėti, kad šiame projekte naudojami ZYBO valdybos apribojimai. Taigi, jei norite vykdyti šį projektą kitoje lentoje, turėtumėte atnaujinti apribojimų failą ir pritaikyti kaiščių skaičių pagal spalvą.

Pažvelkite į figūrą Nr. 2. Atminkite, kad nors mūsų VGA valdiklis išleidžia 5/6 bitus kiekvienai spalvai, prieš pradedant kabelį, šie bitai paverčiami vienu analoginiu signalu kiekvienam spalvų kanalui (raudonai, žaliai ir mėlynai).

4 žingsnis: IŠVESTIS - HDMI valdiklis 1 dalis

Dabar, kai žinome, kaip veikia VGA valdiklis, ir turime darbinį dizainą, galime tęsti su HDMI valdikliu. HDMI valdiklis iš tikrųjų naudos visą kodą, kurį sukūrėme VGA valdiklyje. HDMI ir VGA naudoja tą patį laiką ir tuos pačius signalus. Skirtumas atsiranda ant išėjimo kaiščių.

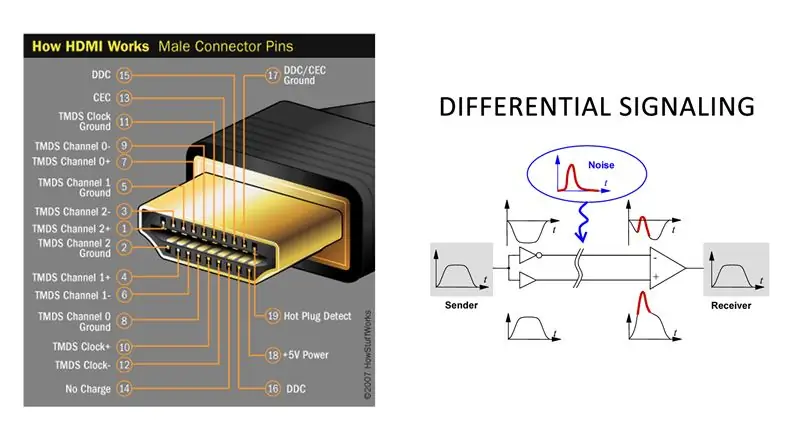

Nors VGA kiekvienai spalvai naudoja vieną laidą ir perduoda analoginį signalą, HDMI perduoda duomenis skaitmeniniu būdu 1 bitą vienu metu kiekvienai spalvai ir naudoja diferencinį signalizavimą. Diferencialinis signalizavimas reiškia, kad kiekvienam bitui HDMI turi 2 kaiščius, kurių vienas yra priešingas kitam. Taigi, jei norėtume perduoti signalą „1“, mes perduodame „1“ant laido, o „1“- neigiamą ant kito laido. Tai užtikrina signalo vientisumą ir daugiau apie jį galite perskaityti čia https://goo.gl/6CPCzB. Mes turime vieną iš šių kanalų kiekvienai spalvai, RAUDONAI, ŽALIAI ir MĖLYNAI, ir vieną laikrodžiui. Dėl diferencinio signalizavimo ypatumų signalai, kuriuos siunčiame per hdmi, turi būti subalansuoti nuolatine srove, o tai reiškia, kad 1 ir 0 skaičius per tam tikrą laiką turi būti maždaug vienodi. Norėdami tai padaryti, naudosime 8b/10b kodavimą. Čia galite sužinoti daug apie tai, kaip veikia diferencinis signalizavimas ir 8b/10b kodavimas iš DVI specifikacijos čia https://goo.gl/hhh8Ge (DVI ir HDMI naudoja tuos pačius vaizdo signalus).

5 žingsnis: IŠVESTIS - HDMI valdiklis 2 dalis

Užteks teorijos, pereikime prie mūsų projekto. Nors VGA valdiklyje mes gavome 148,5 MHz laikrodį, čia turėsime pateikti 10 kartų didesnį dažnį, nes norime perduoti 8 bitus kiekvienai spalvai ir naudojant 8b/10b kodavimą, kuris reiškia 10 bitų pikseliui ir 10 *148,5 MHz = 1485 MHz. Tai didžiulis dažnis, kurio negalima gauti „Zybo“lentoje. Laimei, pasiėmėme keletą gudrybių. Mes galime valdyti 5*148,5 MHz = 742,5 MHz, o mes naudosime OSERDES (serializatoriaus) IP, kad perduotume duomenis tiek kylančiame, tiek krintančiame 742,5 MHz laikrodžio krašte, todėl iš tikrųjų gausime 1485 MHz dažniu perduodamus duomenis. „Vivado“duos mums tam tikrus įspėjimus apie laiką ir visada galite pasirinkti mažesnę skiriamąją gebą su mažesniu laikrodžiu, tačiau kadangi tai veikia, kol kas to tikrai neprieštaraujame (įspėjimai yra susiję su tuo, kad laikrodžio buferiai nėra oficialiai palaiko aukštesnius nei 464 MHz dažnius).

Taigi, ką mes turime padaryti, tai koduoti duomenis iš mūsų VGA valdiklio išvesties 8b/10b formatu ir tada juos serijizuoti, kaip minėta aukščiau. Mes taip pat turėsime pridėti dar vieną MMCM prie projekto, kad sukurtume 742.5MHz laikrodį serijavimui.

Žemiau pridėjau kodavimo ir serijinio įrenginio vhdl failus. Pirmiausia turite užkoduoti RGB kanalus ir tada juos serijuoti.

Raudonojo kanalo pavyzdys:

TMDS_encoder_RED: TMDS_encoder

uosto žemėlapis (clk148, red_channel_8bits, c_red, video_on, encoded_red_10bits);

Serialiser_RED: Serialiser10_1

uosto žemėlapis (clk148, clk742, užkoduoti_ raudoni_10 bitų, atstatyti, red_serial_1bit);

TMDS_encoder įvestis „c“yra „00“raudonai ir žaliai, o „vsync & hsync“- mėlyna (tai yra DVI specifikacijos dalis

6 veiksmas: vaizdų rodymas iš RAM

HDMI valdiklio paskirtis yra parodyti apdorotus vaizdus. Dabar, kai valdiklis yra įdiegtas ir paruoštas naudoti, turėtume galvoti apie šio valdiklio maitinimą duomenimis. Atsižvelgiant į tai, kad daug vaizdo patobulinimų vyks PS (apdorojimo sistema = ARM procesorius), o gauti vaizdai bus DDR atmintyje. Taigi mums reikia būdo gauti duomenis iš RAM į HDMI valdiklį.

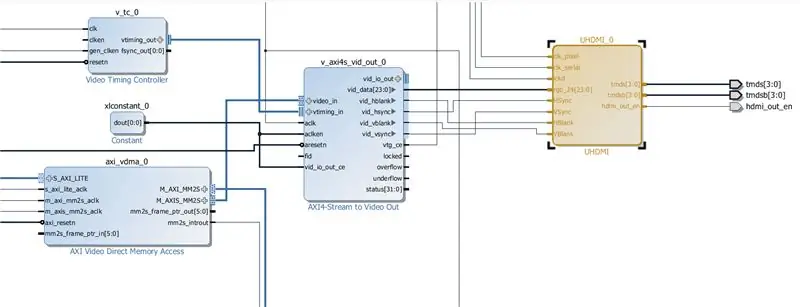

Norėdami tai padaryti, jums reikės 3 IP adresų:

1) VDMA (tiesioginė vaizdo atminties prieiga)

2) VTC (vaizdo laiko valdiklis)

3) Srautas į vaizdo išvestį (nuo šiol tai vadinsime S2VO)

S2VO iš tikrųjų suteiks RGB 24BIT signalą išėjimui ir reikalingus HSYNC ir VSYNC signalus. Taigi mes galime palikti šią HDMI valdiklio dalį.

Turėtumėte pridėti šiuos IP adresus prie savo dizaino, sukonfigūruoti juos ir užmegzti tinkamus ryšius.

Galiausiai turėtumėte gauti kažką panašaus į aukščiau pateiktą schemą.

7 žingsnis: IŠVESTIS - SDK PABAIGA

Kai visa aparatūra yra paruošta ir paruošta naudoti, dabar turime sukurti programinę įrangą PS. Eksportuosime aparatinę įrangą ir bitų srautą ir paleisime SDK.

1) Failas -> Eksportuoti -> Eksportuoti aparatinę įrangą -> Patikrinkite Įtraukti bitų srautą ir paspauskite Gerai

2] Failas -> Paleisti SDK

SDK sukurkite naują programos projektą.

3) Failas -> Naujas -> Taikymo projektas

4) Pasirinkite savo projekto pavadinimą ir paspauskite Pirmyn

5) Pasirinkite šabloną „Labas pasaulis“ir paspauskite Baigti

SDK programai reikės užprogramuoti VDMA. Tam yra naudojamos tam tikros standartinės funkcijos (kai turėsiu laiko, išsamiai išnagrinėsiu).

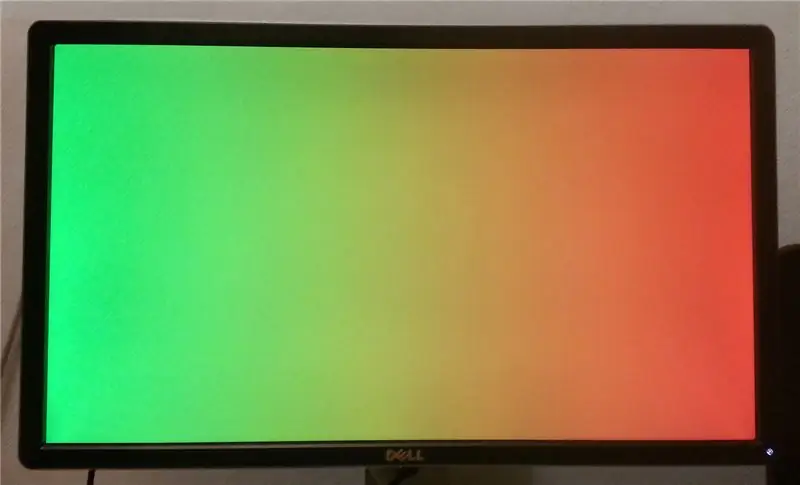

Norėdami išbandyti savo dizainą, mes naudosime SDK atkūrimo („Xilinx Tools“-> „Dump/Restore“) funkciją, norėdami įdėti vaizdą į DDR RAM atmintį ir parodyti jį naudodami mūsų HDMI valdiklį. Vaizdą galite įkelti bet kur, kur tik norite (išskyrus kai kurias mažas ribotas sritis atminties pradžioje). Pavyzdžiui, pasirinkome adresą 16777216 ir failo dydį 8294400 = 1920*1080*4 (4 kanalai = RGB + alfa).

Tai veikia !

Tęsti reikia

Rekomenduojamas:

Vaizdo apdorojimo pagrindu sukurta gaisro atpažinimo ir gesintuvo sistema: 3 žingsniai

Vaizdo apdorojimo pagrindu sukurta gaisro atpažinimo ir gesintuvo sistema: Sveiki draugai, tai vaizdo apdorojimu pagrįsta gaisro aptikimo ir gesintuvo sistema naudojant „Arduino“

Vaizdo apdorojimas naudojant „Raspberry Pi“: „OpenCV“ir vaizdo spalvų atskyrimo diegimas: 4 veiksmai

Vaizdo apdorojimas naudojant „Raspberry Pi“: „OpenCV“ir vaizdo spalvų atskyrimo diegimas: Šis įrašas yra pirmasis iš kelių vaizdo apdorojimo vadovėlių, kurie turi būti sekami. Mes atidžiau pažvelgsime į vaizdo taškus, sudarančius vaizdą, sužinosime, kaip įdiegti „OpenCV“į „Raspberry Pi“, taip pat rašome bandomuosius scenarijus, kad galėtume užfiksuoti vaizdą ir

Tiesioginė 4G/5G HD vaizdo transliacija iš DJI drono esant mažai delsai [3 žingsniai]: 3 žingsniai

![Tiesioginė 4G/5G HD vaizdo transliacija iš DJI drono esant mažai delsai [3 žingsniai]: 3 žingsniai Tiesioginė 4G/5G HD vaizdo transliacija iš DJI drono esant mažai delsai [3 žingsniai]: 3 žingsniai](https://i.howwhatproduce.com/images/009/image-25904-j.webp)

Tiesioginis 4G/5G HD vaizdo įrašų srautinis perdavimas iš DJI drono esant mažai delsai [3 žingsniai]: Šis vadovas padės jums gauti tiesioginius HD kokybės vaizdo srautus iš beveik visų DJI dronų. Naudodami „FlytOS Mobile App“ir „FlytNow Web Application“galite pradėti transliuoti vaizdo įrašus iš drono

Vaizdo žaidimas „Saugos sistema“: 15 žingsnių

Vaizdo žaidimas „Apsaugos sistema“: taip galite sukurti paprastą platformingą „flowlab.io“. Žaidimą, naudojamą kaip pavyzdys šioje pamokoje, galima žaisti, o jo programavimą peržiūrėti ir redaguoti (bet neišsaugoti) šioje nuorodoje: https: // flowlab.io/game/play/1130006

Paprastas vaizdo kameros vaizdo ieškiklio įsilaužimas: 11 žingsnių (su nuotraukomis)

Paprastas vaizdo kameros vaizdo ieškiklio įsilaužimas: šiandien aš jus išmokysiu nulaužti vaizdo kameros vaizdo ieškiklį! (Čia aš turiu savo vaizdo ieškiklį šalia Raspberry Pi) Tai yra pagrindinis I/O bandymų ekranas. Jį galite naudoti viskam, kas skleidžia sudėtinį vaizdo signalą, pvz., „Raspberry Pi“(Nuostabiam