Turinys:

- Autorius John Day day@howwhatproduce.com.

- Public 2024-01-30 10:45.

- Paskutinį kartą keistas 2025-01-23 14:59.

Prijunkite „Mojo“kūrimo plokštę prie išorinių įėjimų naudodami šį skydą.

Kas yra „Mojo“plėtros lenta?

„Mojo“plėtros lenta yra kūrimo lenta, pagrįsta „Xilinx spartan 3 FPGA“. Lentą pagamino „Alchitry“. FPGA yra labai naudingi, kai vienu metu turi būti vykdomi keli procesai.

Ko jums reikės?

Prekės

„Mojo“plėtros lenta

Gerber failas

8 x 15k omų rezistoriai (neprivaloma*)

4 x 470 omų rezistoriai

4 x 560 omų rezistoriai

4 x CC septynių segmentų ekranai

4 x 3 mm šviesos diodai

4 x liečiami SPDT jungikliai

1 x 4 padėties paviršiaus tvirtinimo DIP jungiklis

2 x 25 x 2 arba 4 x 25 antraštės

1x 2 x 5 kontaktų dėžutės galvutė

Lituoklis

Lituoklis

Flux

*(jei šie rezistoriai praleisti, reikia įjungti atitinkamą kaištį)

1 veiksmas: įkelkite „Gerber“į savo pasirinktą kompiuterio gamintoją

Savo plokštėms užsisakiau iš JLC PCB.

Vienintelis pakeitimas buvo spalva, kurią norėjau suderinti su „Mojo“juoda spalva.

2 žingsnis: valdybos surinkimas

Lituodamas visada manau, kad pirmiausia naudinga lituoti žemiausias dalis, todėl pradėti nuo rezistorių yra gera idėja.

R5, R6, R7, R8, R9, R10, R11 ir R12 yra 15 k omų rezistoriai, naudojami jungikliams nuspausti (jei naudojate vidinį ištraukimą/ištraukimą, ignoruokite tai).

R1, R2, R3, R4 yra 560 omų rezistoriai, kurie yra atsakingi už srovės ribojimą per 7 segmentų ekraną.

R13, R14, R15, R16 yra 470 omų rezistoriai, kurie yra atsakingi už srovės apribojimą per 4 šviesos diodus.

Toliau lituokite panardinimo jungiklį, lytėjimo jungiklius, šviesos diodus, septynių segmentų ekranus ir dėžutės antraštės jungtį tokia tvarka.

Dabar įdėkite 25 x 2 (arba 2 25 x 1) į mojo, kad sulygintumėte kaiščius. Sulygiuokite skydą su kaiščiais ir lituokite.

3 veiksmas: programinės įrangos sąranka

Programinė įranga, nurodyta „Alchitry“svetainėje, praneš jums, ko jums reikia norint pradėti ir įdiegti „Xilinx ISE“. Tačiau pakeiskite.ucf failą, kad jis žinotų, kokie kaiščiai yra prijungti prie to, kas svarbu jūsų programai paleisti.

Čia yra.ucf failas, kurį naudoju su skydu:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARDAS = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARDAS = LVTTL; NET "cclk" LOC = P70 | IOSTANDARDAS = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARDAS = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARDAS = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARDAS = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARDAS = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARDAS = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARDAS = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARDAS = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARDAS = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARDAS = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARDAS = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARDAS = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARDAS = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARDAS = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARDAS = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARDAS = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARDAS = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARDAS = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARDAS = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARDAS = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARDAS = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARDAS = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARDAS = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARDAS = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARDAS = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARDAS = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARDAS = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARDAS = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARDAS = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARDAS = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARDAS = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARDAS = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARDAS = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARDAS = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARDAS = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARDAS = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARDAS = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARDAS = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARDAS = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARDAS = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARDAS = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARDAS = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARDAS = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARDAS = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARDAS = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARDAS = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARDAS = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARDAS = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARDAS = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARDAS = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARDAS = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARDAS = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARDAS = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARDAS = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARDAS = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARDAS = LVTTL;

Prisiminkite, jei neįdiegėte išskleidžiamųjų rezistorių, kad galėtumėte redaguoti.ucf kaiščius naudodami

| PULLDOWN; o

| PULLUP;

Jei norite bloką naudoti bet kam, jungtys yra tokios. Kairysis yra bloko kaiščio numeris, o dešinysis - mojo kaiščio numeris, kurį turėtumėte priskirti savo.ucf:

1 kaištis = 29

2 kaištis = 51

3 kaištis = 32

4 kaištis = 41

5 kaištis = 34

6 kaištis = 35

kaištis 7 = 40

8 kaištis = 33

9 kaištis = GND

kaištis 10 = +V.

Rekomenduojamas:

„FPGA Cyclone IV DueProLogic Controls“„Raspberry Pi“kamera: 5 žingsniai

„FPGA Cyclone IV DueProLogic Controls“„Raspberry Pi“fotoaparatas: Nepaisant to, kad „FPGA DueProLogic“yra oficialiai sukurta „Arduino“, mes ketiname padaryti FPGA ir „Raspberry Pi 4B“perduodamus. Šioje pamokoje įgyvendinamos trys užduotys: (A) Vienu metu paspauskite du mygtukus FPGA, norint pasukti kampą

FPGA Cyclone IV DueProLogic - mygtukas ir LED: 5 žingsniai

„FPGA Cyclone IV DueProLogic“- mygtukas ir šviesos diodas: šioje pamokoje mes naudosime FPGA išorinei šviesos diodų grandinei valdyti. Mes ketiname įgyvendinti šias užduotis (A) Norėdami valdyti šviesos diodus, naudokite „FPGA Cyclone IV DuePrologic“mygtukus. (B) Blykstės šviesos diodas šviečia & periodiškai išjungta Vaizdo demonstracinė laboratorija

„FPGA Cyclone IV DueProLogic Controls“servo variklis: 4 žingsniai

„FPGA Cyclone IV DueProLogic Controls Servo Motor“: šioje pamokoje mes parašysime „Verilog“kodą, skirtą valdyti servo variklį. Servo SG-90 gamina „Waveshare“. Pirkdami servo variklį, galite gauti duomenų lapą, kuriame nurodoma darbinė įtampa, maksimalus sukimo momentas ir siūlomas variklio

WIDI - belaidis HDMI naudojant „Zybo“(„Zynq Development Board“): 9 žingsniai (su paveikslėliais)

WIDI - belaidis HDMI naudojant „Zybo“(„Zynq Development Board“): ar kada nors norėjote, kad galėtumėte prijungti televizorių prie kompiuterio ar nešiojamojo kompiuterio kaip išorinio monitoriaus, bet nenorėjote, kad visi šie erzinantys laidai netrukdytų? Jei taip, ši pamoka kaip tik jums! Nors yra keletas produktų, kurie pasiekia šį tikslą

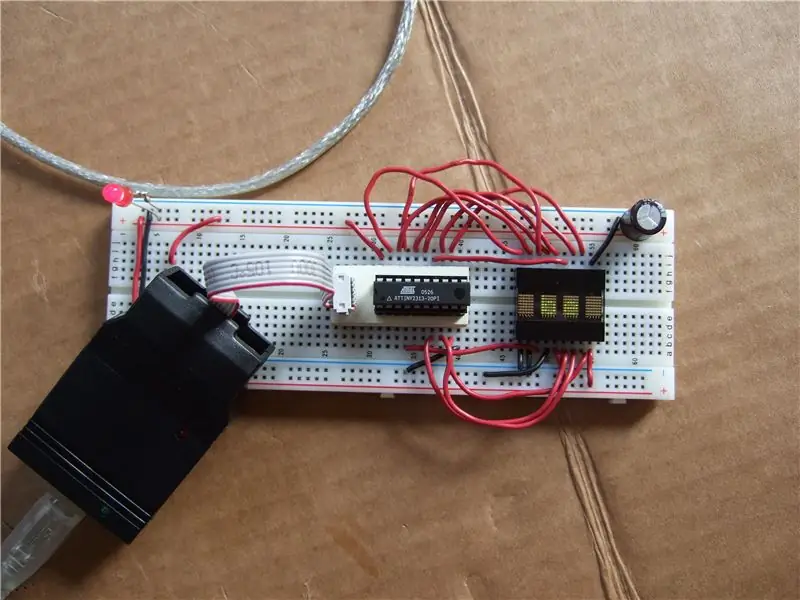

„Ghetto Development Environment“: 5 žingsniai

„Ghetto Development Environment“: prieš kurį laiką paskelbiau greitą ir purviną „el cheapo“; „Atmel AVR“serijos lustų programavimo pradžios metodas: „Ghetto Programmer“(1.0 versija). Galvojau, kad bus